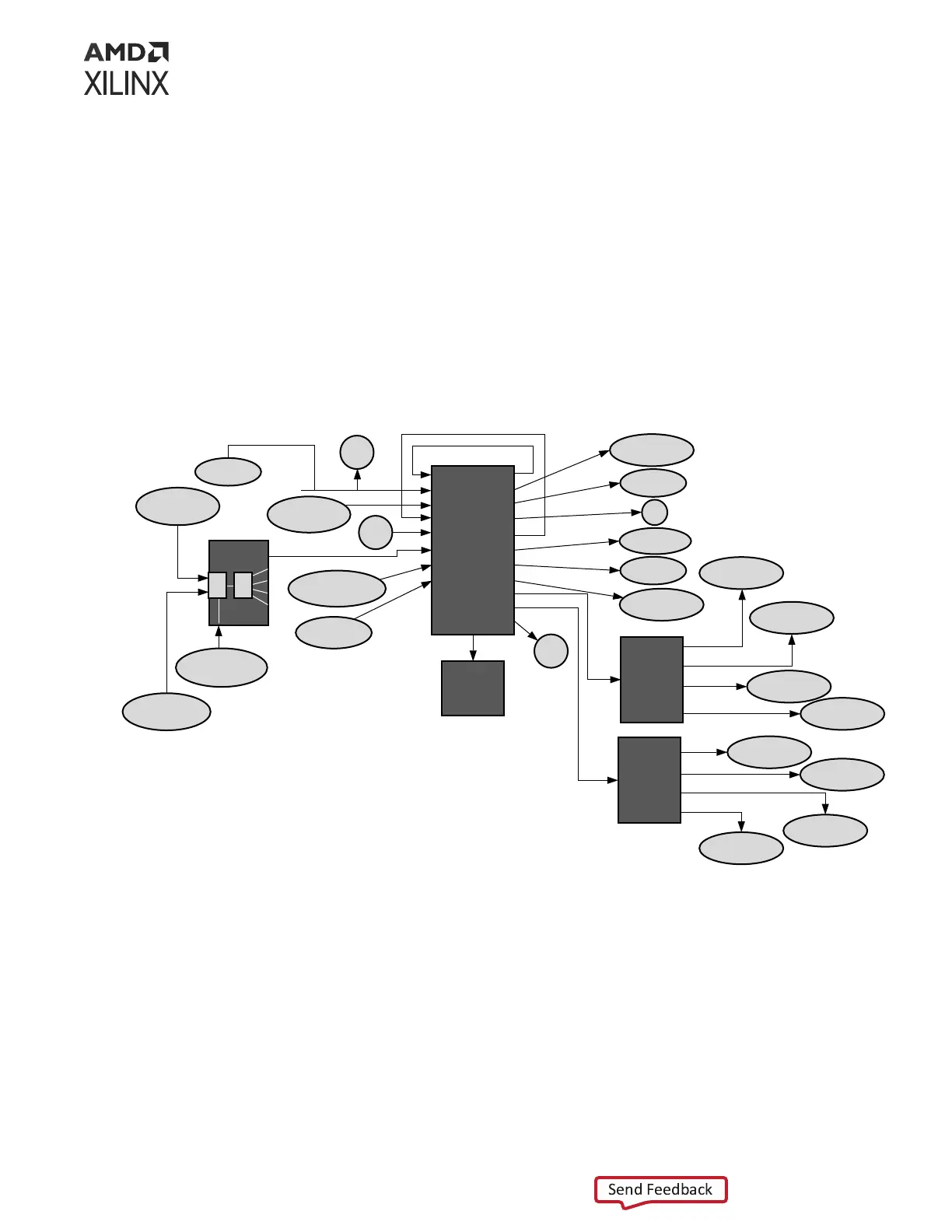

IEEE-1588 eCPRI Programmable Synchronization Management Unit

[Figure 3, callout 46]

The 8A34001 synchronizaon management unit (SMU) provides tools to manage ming

references, clock sources, and ming paths for IEEE 1588 and Synchronous Ethernet (SyncE)

based clocks. The PLL channels can act independently as frequency synthesizers, jier

aenuators, digitally controlled oscillators (DCO), or digital phase lock loops (DPLL). The

following block diagram can aid in quickly determining the overall clock tree for the 8A34001

(U219). See schemac pages 90-91 for details. For more details on programming and controlling

the 8A34001, see the Renesas/Integrated Device Technology, Inc. (IDT) website and data sheet.

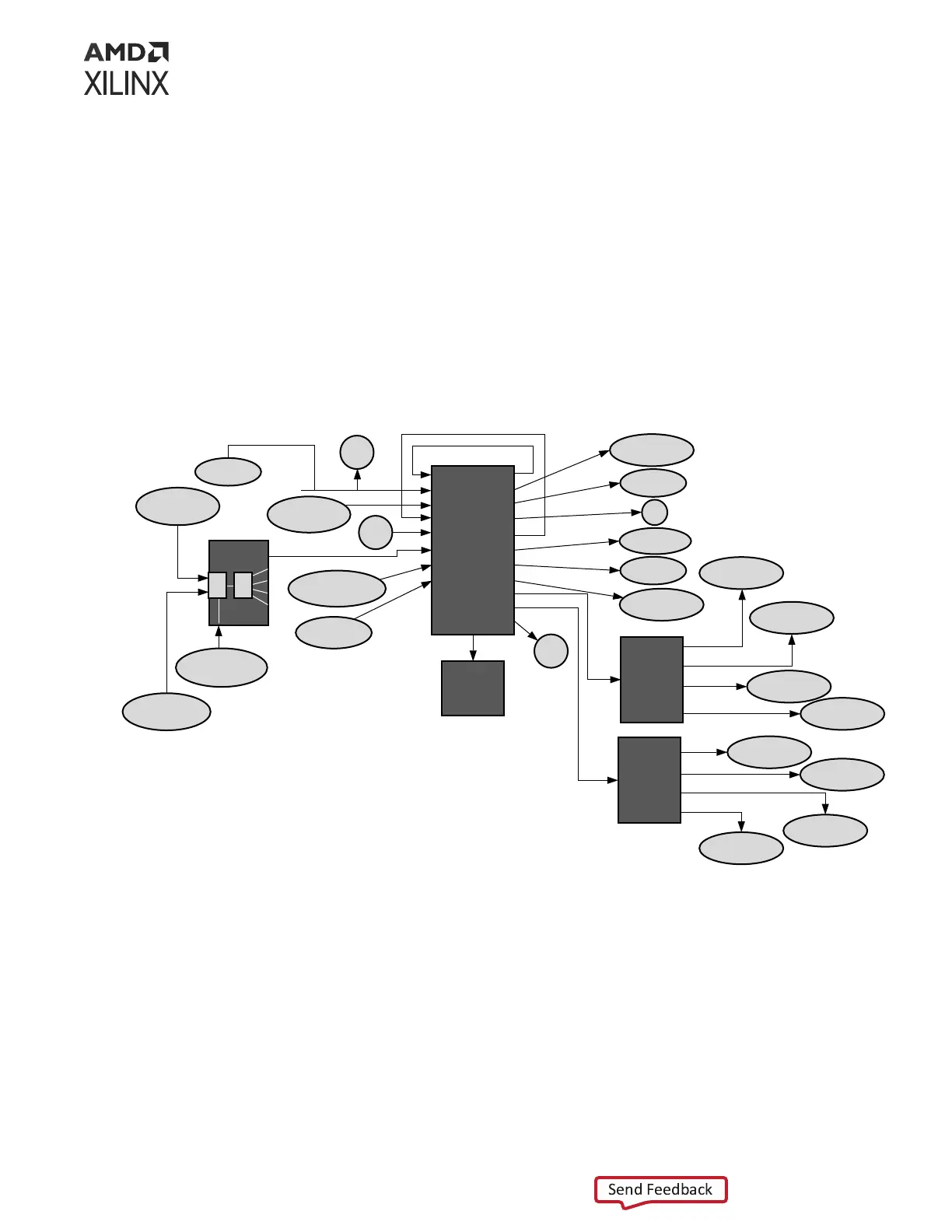

Figure 18: IEEE-1588 eCPRI Block Diagram

8P34S1204

8A34001

0x5B

Versal ACAP

Bank 221:

GTM REFCLK1

Versal ACAP

Bank 121:

GTM REFCLK1

Versal ACAP

Bank 711

Versal ACAP

Bank 219:

GTM_TX2

Versal ACAP

Bank 219:

GTM REFCLK1

FMC:

REFCLK_M2C

Versal ACAP

Bank 703

Versal ACAP

Bank 219:

GTM_RX2

Versal ACAP

Bank 703

FMC:

REFCLK_C2M

Versal ACAP

Bank 712

Versal ACAP

Bank 219:

GTM_REFCLK0

Versal ACAP

Bank 124:

GTM_REFCLKP0

Versal ACAP

Bank 122:

GTM_REFCLKP0

Versal ACAP

Bank 224:

GTM_REFCLKP0

Versal ACAP

Bank 221:

GTM_REFCLKP0

SMA

J338

SMA

J330

J331

SMA

J328

J329

SMA

J339

CLK0

CLK1N

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

I2C MR_N

24FC1025

EEPROM

128K

0x54

8P34S11024

Clock

Buffer

QSFP_SEL

Sel

X4

buff

Q8_BUF0

Versal ACAP

Bank 121:

GTM_REFCLKP0

Versal ACAP

Bank 123:

GTM_REFCLKP0

Q8_BUF1

Q8_BUF2

Q8_BUF3

Versal ACAP

Bank 223:

GTM_REFCLKP0

Versal ACAP

Bank 222:

GTM_REFCLKP0

Q9_BUF0

8P34S11024

Clock

Buffer

Q9_BUF1

Q9_BUF2

Q9_BUF3

X27272-101222

Transceivers

The Versal ACAP has 168 PL transceivers including 28 GTYP and 140 GTM type transceivers.

The following table contains the mapping to hardened features, quads, channel locaons, as well

as general features.

Chapter 3: Board Component Descriptions

UG1582 (v1.0) February 21, 2023 www.xilinx.com

VPK180 Board User Guide 49

Loading...

Loading...