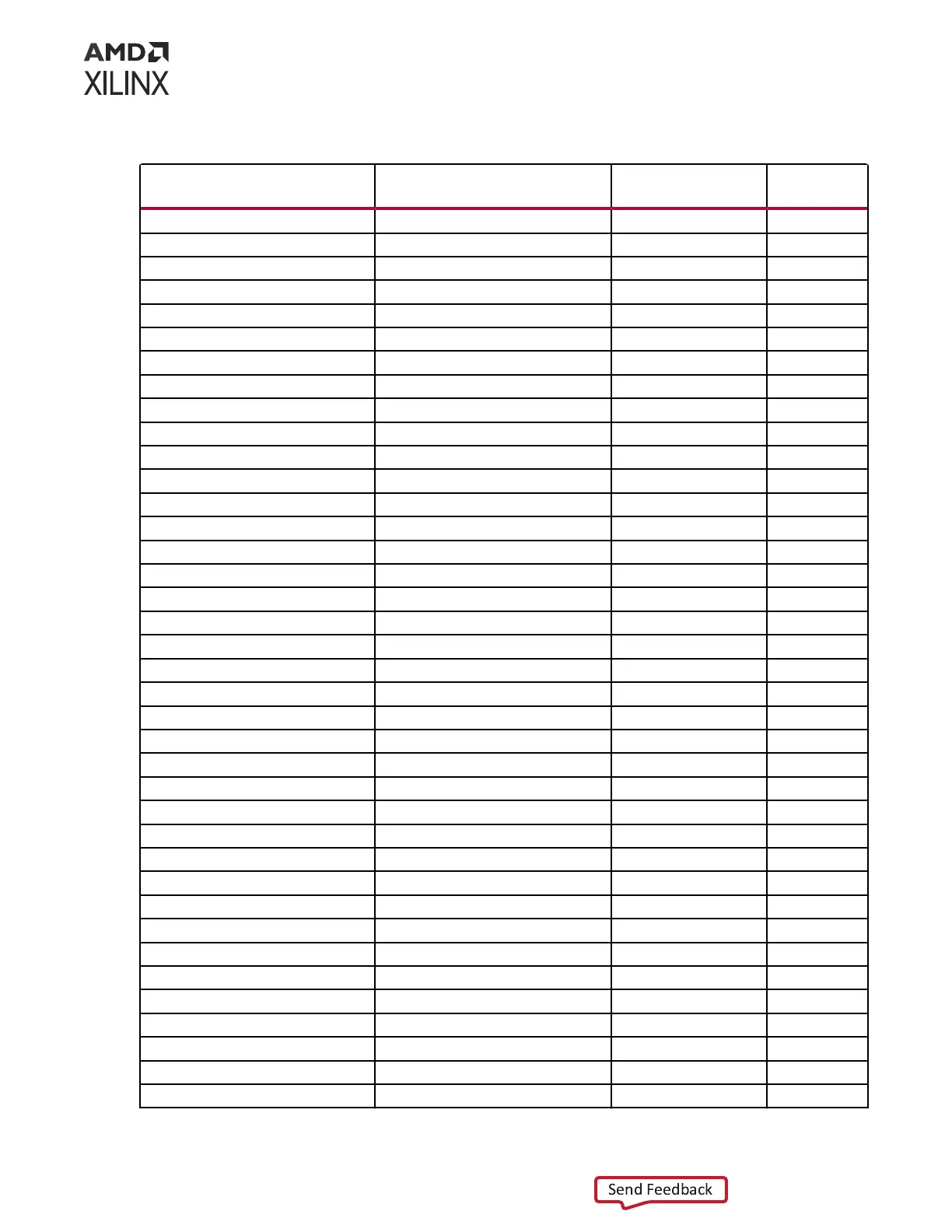

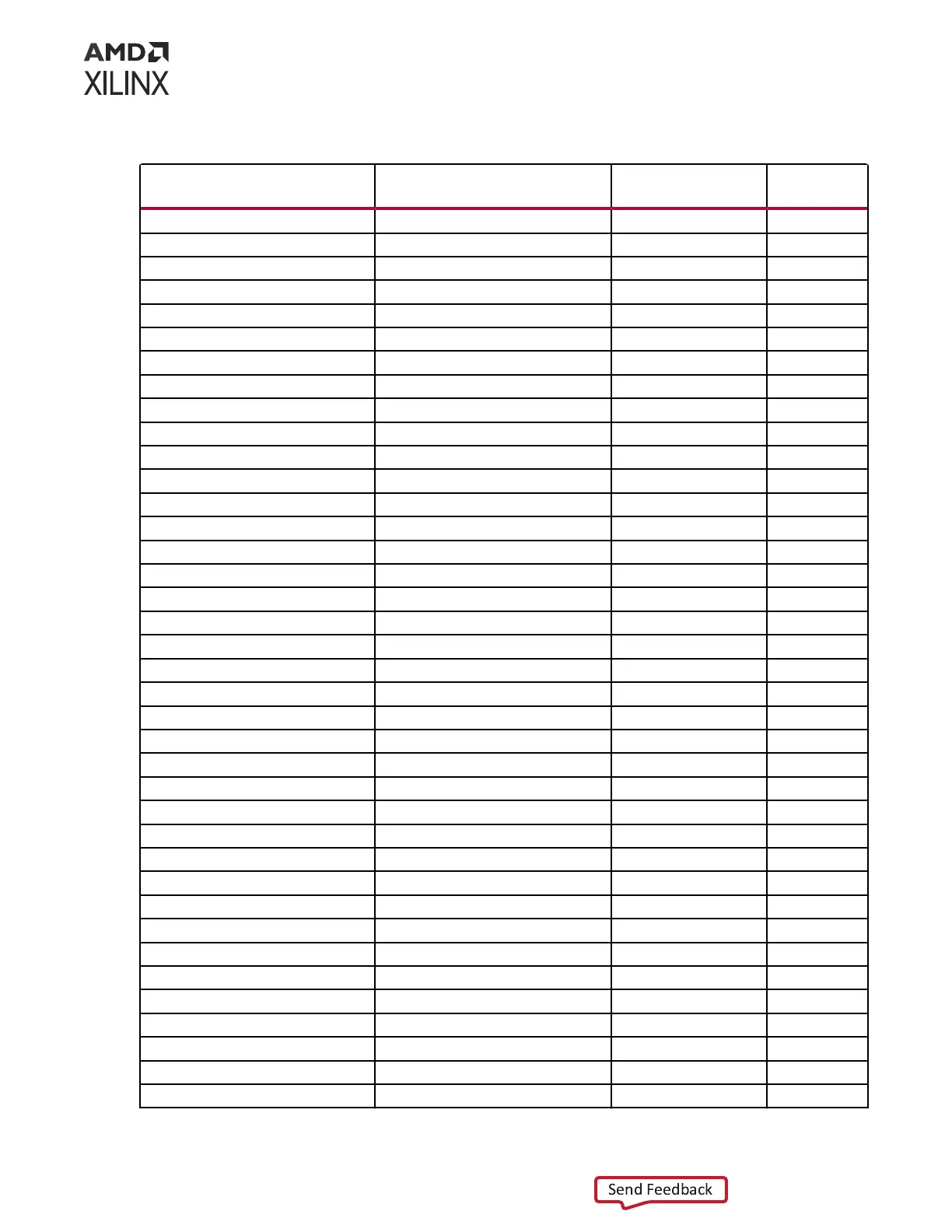

Table 18: Transceiver Module Control Signals (cont'd)

Signal Name Feature Notes

Schematic

Page

QSFPDD1_MODSELL Module select U233 P00 6, 55, 57

QSFPDD1_RESETL Module reset U1 Bank 711 6, 57

QSFPDD1_MODPRSL Module present U1 Bank 711 6, 57

QSFPDD1_INTL Interrupt U1 Bank 711 6, 57

QSFPDD1_INITMODE Low power mode U1 Bank 711 6, 57

QSFPDD2_MODSELL Module select U233 P01 6, 55, 57

QSFPDD2_RESETL Module reset U1 Bank 711 6, 57

QSFPDD2_MODPRSL Module present U1 Bank 711 6, 57

QSFPDD2_INTL Interrupt U1 Bank 711 6, 57

QSFPDD2_INITMODE Low power mode U1 Bank 711 6, 57

QSFPDD3_MODSELL Module select U233 P02 6, 55, 58

QSFPDD3_RESETL Module reset U1 Bank 711 6, 58

QSFPDD3_MODPRSL Module present U1 Bank 711 6, 58

QSFPDD3_INTL Interrupt U1 Bank 711 6, 58

QSFPDD3_INITMODE Low power mode U1 Bank 711 6, 58

QSFPDD4_MODSELL Module select U233 P03 6, 55, 58

QSFPDD4_RESETL Module reset U1 Bank 711 6, 58

QSFPDD4_MODPRSL Module present U1 Bank 711 6, 58

QSFPDD4_INTL Interrupt U1 Bank 711 6, 58

QSFPDD4_INITMODE Low power mode U1 Bank 711 6, 58

QSFPDD5_MODSELL Module select U233 P05 6, 55, 59

QSFPDD5_RESETL Module reset U1 Bank 711 6, 59

QSFPDD5_MODPRSL Module present U1 Bank 711 6, 59

QSFPDD5_INTL Interrupt U1 Bank 711 6, 59

QSFPDD5_INITMODE Low power mode U1 Bank 711 6, 59

QSFPDD6_MODSELL Module select U233 P06 6, 55, 59

QSFPDD6_RESETL Module reset U1 Bank 711 6, 59

QSFPDD6_MODPRSL Module present U1 Bank 711 6, 59

QSFPDD6_INTL Interrupt U1 Bank 711 6, 59

QSFPDD6_INITMODE Low power mode U1 Bank 711 6, 59

OSFP_I2C_SDA Two-wire interface data U35 I2C MUX 56, 60

OSFP_I2C_SCL Two-wire interface clock U35 I2C MUX 56, 60

OSFP_H_LPWN_N U1 to module low power mode U2 level shift 7, 57, 60

OSFP_H_PRS_N Module to U1 module present U9 level shift 7, 57, 60

OSFP_H_INTN Module to U1 interrupt U9 level shift 7, 57, 60

OSFP_H_RSTN U1 to module reset U2 level shift 7, 57, 60

SFPDD1_I2C_SDA Two-wire interface data U322 I2C MUX 56, 63

SFPDD1_I2C_SCL Two-wire interface clock U322 I2C MUX 56, 63

Chapter 3: Board Component Descriptions

UG1582 (v1.0) February 21, 2023 www.xilinx.com

VPK180 Board User Guide 60

Loading...

Loading...