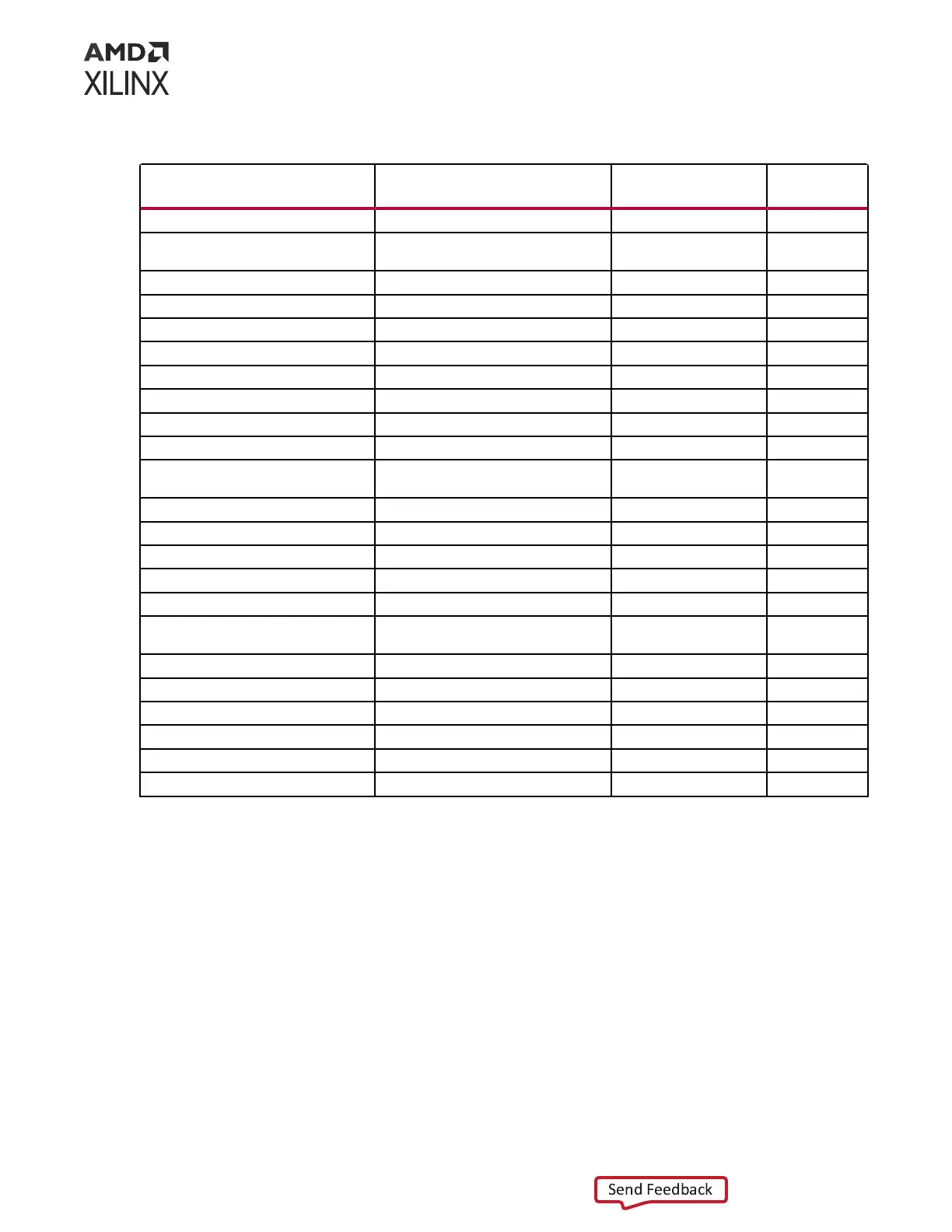

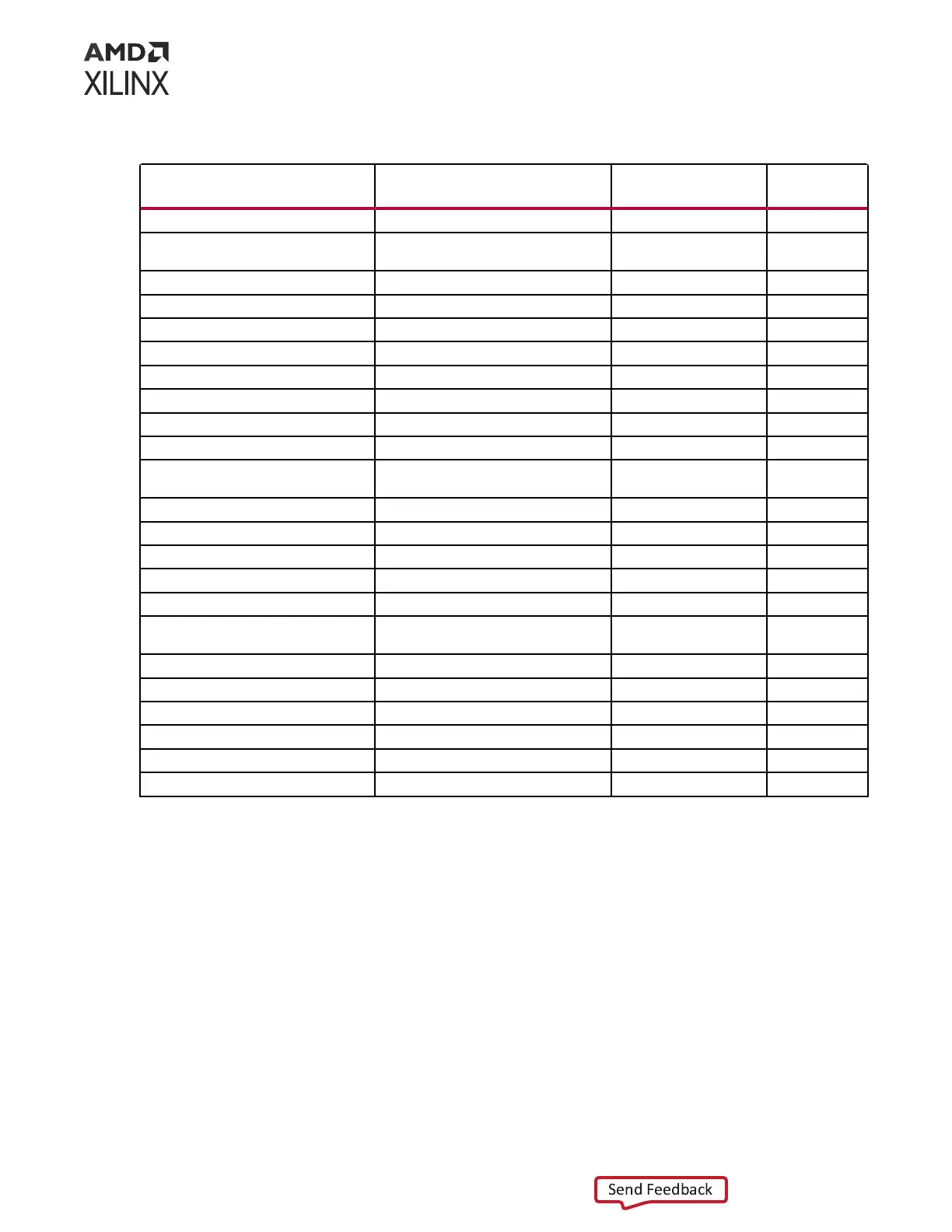

Table 18: Transceiver Module Control Signals (cont'd)

Signal Name Feature Notes

Schematic

Page

SFPDD3_CH1_TXFAULTDD U1 to module - transmitter disable U1 Bank 710 6, 64

SFPDD3_CH1_TXDISABLEDD Module to U1 - fault condition

interrupt/detected

U1 Bank 710 6, 64

SFPDD3_CH1_SPEED1DD Module receive - rate selection Float on board 64

SFPDD3_CH1_SPEED2DD Module receive - rate selection Float on board 64

SFPDD3_CH1_RXLOSDD Module to U1 - RX signal loss U1 Bank 710 6, 64

SFPDD3_MOD_ABS Module to U1 - module absent U1 Bank 710 6, 64

SFPDD3_LPMODE U1 to module - low power mode Float on board 64

SFPDD3_RESETL U1 to module - complete module reset U1 Bank 710 6, 64

SFPDD4_I2C_SDA Two-wire interface data U322 I2C MUX 56, 64

SFPDD4_I2C_SCL Two-wire interface clock U322 I2C MUX 56, 64

SFPDD4_CH0_TXFAULT Module to U1 - fault condition

detected

U1 Bank 710 6, 64

SFPDD4_CH0_TXDISABLE U1 to module - transmitter disable U1 Bank 710 6, 64

SFPDD4_CH0_SPEED1 Module receive rate selection Float on board 64

SFPDD4_CH0_SPEED2 Module receive rate selection Float on board 64

SFPDD4_CH0_RXLOS Module to U1 - RX signal loss U1 Bank 710 6, 64

SFPDD4_CH1_TXFAULTDD U1 to module - transmitter disable U1 Bank 710 6, 64

SFPDD4_CH1_TXDISABLEDD Module to U1 - fault condition

interrupt/detected

U1 Bank 710 6, 64

SFPDD4_CH1_SPEED1DD Module receive - rate selection Float on board 64

SFPDD4_CH1_SPEED2DD Module receive - rate selection Float on board 64

SFPDD4_CH1_RXLOSDD Module to U1 - RX signal loss U1 Bank 710 6, 64

SFPDD4_MOD_ABS Module to U1 - module absent U1 Bank 710 6, 64

SFPDD4_LPMODE U1 to module - low power mode Float on board 64

SFPDD4_RESETL U1 to module - complete module reset U1 Bank 710 6, 64

High-speed Debug Port

The PS includes an integrated Aurora 64B/66B block that is dedicated for accessing the debug

packet controller (DPC) via a high-speed GT-based interface. This protocol to access the DPC is

the high-speed debug port (HSDP) protocol. The HSDP provides bidireconal access to the

device from an external host debug/trace module, allowing for high-speed debug and trace

operaons. The SmartLynq+ module can be connected to the Aurora interface to access the

HSDP in the Versal ACAP. For more informaon, see the SmartLynq+ Module User Guide

(UG1514). For informaon on the HSDP quad availability, see the Versal ACAP Technical Reference

Manual (AM011)).

Note: The VPK180 evaluaon board has addional HSDP lanes provided for future System Controller use.

Chapter 3: Board Component Descriptions

UG1582 (v1.0) February 21, 2023 www.xilinx.com

VPK180 Board User Guide 62

Loading...

Loading...