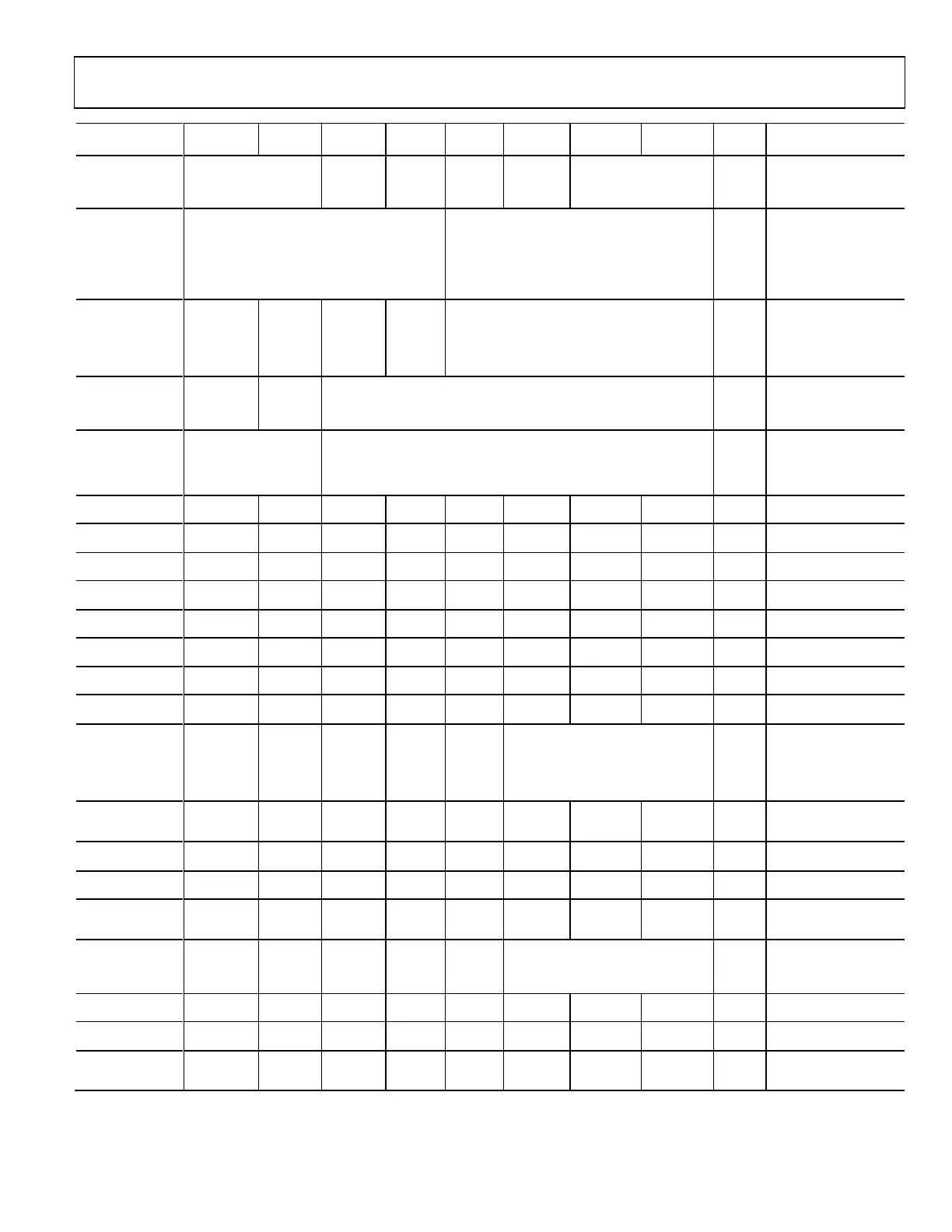

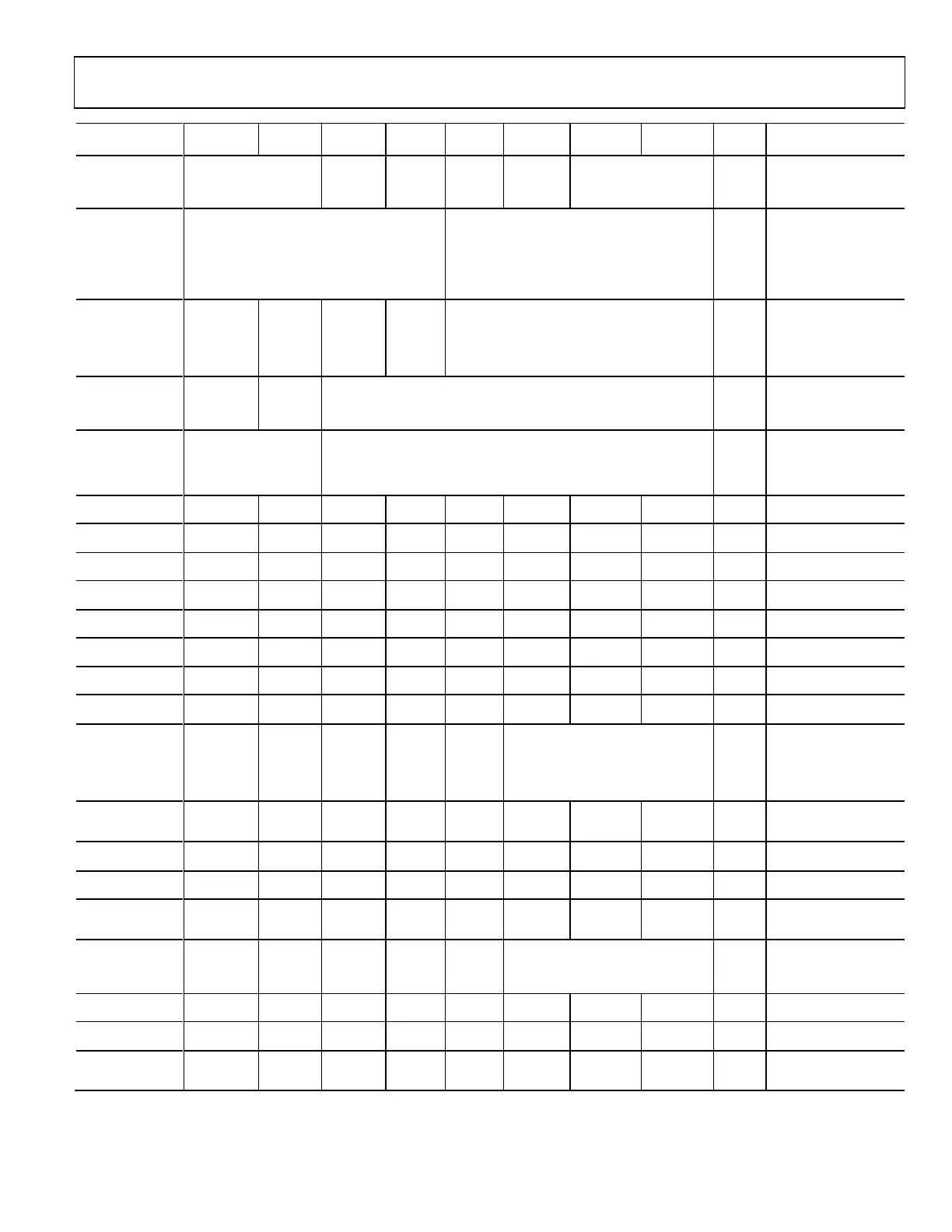

Application Note AN-877

Rev. B | Page 19 of 20

1

Default

Value

1

14, OUTPUT_MODE

0: Level Option 0

1: Level Option 1

2: Level Option 2

3: Level Option 3

Output

mux

enable

Output

enable

DDR

enable

Output

invert

0: Offset binary

1: Twos complement

2: Gray code

3: Reserved

Device

specific

Configures the outputs

and the format of the data.

15,

OUTPUT_ADJUST

Output driver termination; Bits[7:4]

Output driver current; Bits[3:0]

Device

specific

Determines LVDS or other

output properties.

Primarily functions to set

the LVDS span and

common-mode levels in

place of an exte rnal

resistor.

16, OUTPUT_PHASE

Output

polarity

Output clock phase adjust; Bits[3:0] 00h

On devices that utilize

clock divide, determines

which phase of the divider

output is used to supply

the output clock. Internal

latching is unaffected.

17, OUTPUT_DELA Y Enable

DLL

enable

6-bit output delay; Bits[5:0] 00h

This sets the fine output

delay of the output clock

but does not change

internal timing.

18, VREF

V

R EF

select

0: primary (0)

1: secondary (1)

2: Option 2

3: Option 3

6-bit internal V

R EF

adjustment; Bits[5:0] 20h Select and/or adjust the V

R EF

.

19,

B7 B6 B5 B4 B3 B2 B1 B0 00h User-Defined Pattern 1 LSB.

1A,

USER_ PA TT1_MSB

B15 B14 B13 B12 B11 B10 B9 B8 00h User-Defined Pattern 1 MSB.

1B,

USER_ PA TT2_LSB

B7 B6 B5 B4 B3 B2 B1 B0 00h User-Defined Pattern 2 LSB.

1C,

USER_ PA TT2_MSB

B15 B14 B13 B12 B11 B10 B9 B8 00h User-Defined Pattern 2 MSB.

1D,

USER_ PA TT3_LSB

B7 B6 B5 B4 B3 B2 B1 B0 00h User-Defined Pattern 3 LSB.

1E,

USER_ PA TT3_MSB

B15 B14 B13 B12 B11 B10 B9 B8 00h User-Defined Pattern 3 MSB.

1F,

USER_ PA TT4_LSB

B7 B6 B5 B4 B3 B2 B1 B0 00h User-Defined Pattern 4 LSB.

USER_ PA TT4_MSB

B15 B14 B13 B12 B11 B10 B9 B8 00h User-Defined Pattern 4 MSB.

SERIAL_CONTROL

LSB first

optimize

001: 8 bits

010: 10 bits

011: 12 bits

100: 14 bits

101: 16 bits

00h

Default causes MSB first

and the native bit stream.

22,

SERIAL_CH_ STAT

Ch output

reset

Ch

power-

down

00h

Used to power down

individual sections of a

converter (local).

24, MISR_LSB B7 B6 B5 B4 B3 B2 B1 B0 00h

Least significant byte of

MISR (re ad-only).

25, MISR_MSB B15 B14 B13 B12 B11 B10 B9 B8 00h

Most significant byte of

MISR (re ad-only).

2A, FEA TURES

OVR

alternate

pin

OVR output

enable

00h

Auxiliary feature set

control.

2B, HIGH_PASS Tune

Corner frequency

000: dc

000 through 111: Alternate corner

frequencies

00h High-pass filter control.

2C, AIN

Input

impedance

00h Analog input control.

2D, CROSS_POINT 00h

switch.

FF, DEVICE_UPDATE

transfer

SW transfe r 00h

data from the master shift

register to the slave.

1

Hexadecimal.

2

Not supported on most devices.

Loading...

Loading...