ATtiny10/11/12

27

•

Bits 3, 2 - Res: Reserved bits

These bits are reserved bits in the ATtiny10/11/12 and always read as zero.

•

Bits 1, 0 - ISC01, ISC00: Interrupt Sense Control0 bit 1 and bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are

set. The following table shows how to set the ISC bits to generate an external interrupt:

Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK Register.

Otherwise, an interrupt can occur when the bits are changed.

The value on the INT0 pin is sampled before detecting edges. If edge interrupt is selected, pulses that last longer than one

CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level inter-

rupt is selected, the low level must be held until the completion of the currently executing instruction to generate an

interrupt. If enabled, a level-triggered interrupt will generate an interrupt request as long as the pin is held low.

Sleep Modes for the ATtiny10/11

To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. The SM bit

in the MCUCR register selects which sleep mode (Idle or Power-down) will be activated by the SLEEP instruction. If an

enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine, and resumes

execution from the instruction following SLEEP. On wake-up from Power-down Mode on pin change, the two instructions

following SLEEP are executed before the pin change interrupt routine. The contents of the register file and I/O memory are

unaltered. If a reset occurs during Sleep Mode, the MCU wakes up and executes from the Reset vector.

Idle Mode

When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode, stopping the CPU but allowing

Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external

triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog Reset. If wake-up from the Analog

Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog

Comparator Control and Status register – ACSR. This will reduce power consumption in Idle Mode. When the MCU wakes

up from Idle mode, the CPU starts program execution immediately.

Power-down Mode

When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power-down Mode. In this mode, the external

oscillator is stopped, while the external interrupts and the Watchdog (if enabled) continue operating. Only an external reset,

a watchdog reset (if enabled), an external level interrupt, or an pin change interrupt can wake up the MCU.

Note that if a level-triggered or pin change interrupt is used for wake-up from power-down, the changed level must be held

for a time longer than the reset delay period of t

TOUT

. Otherwise, the MCU will fail to wake up.

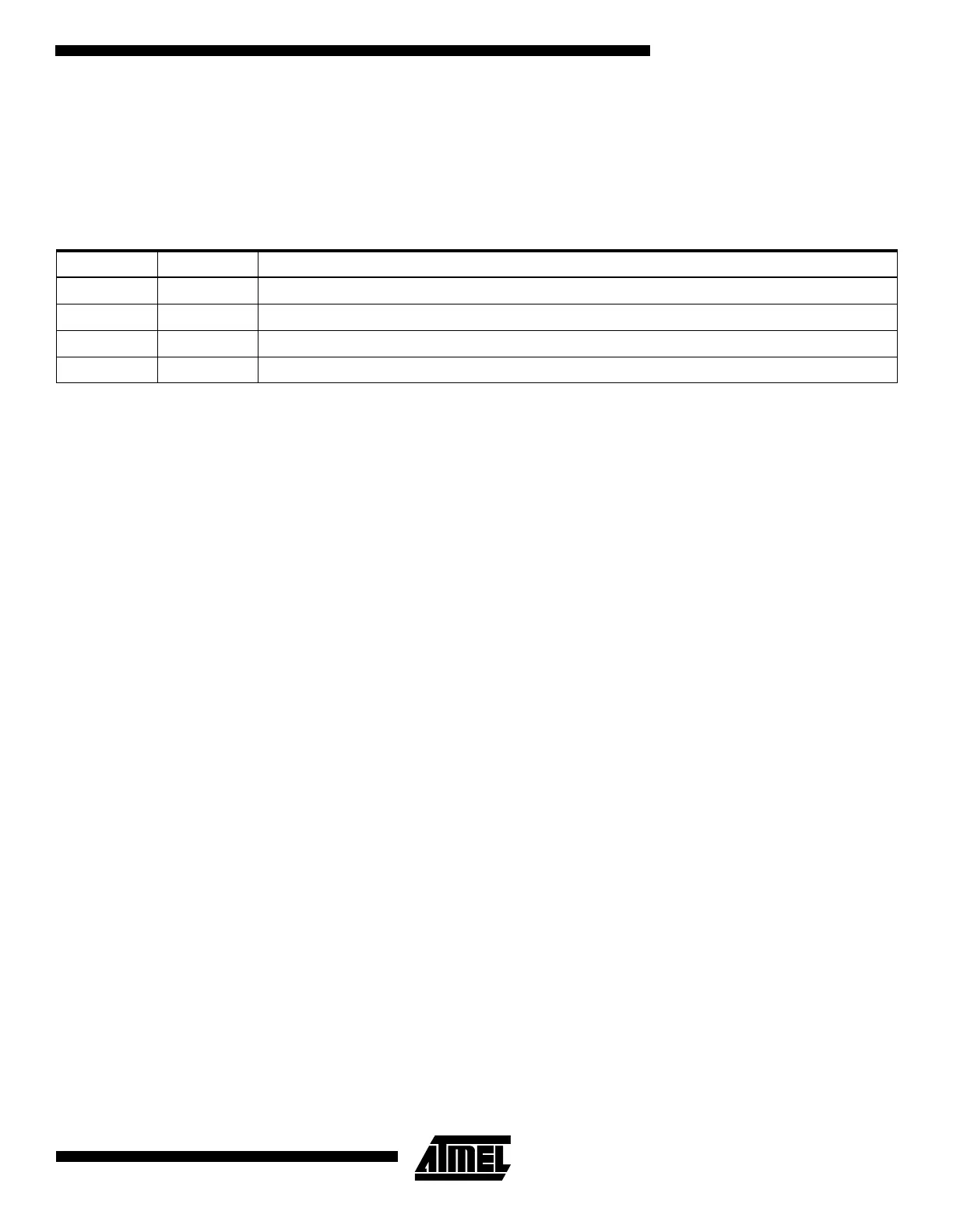

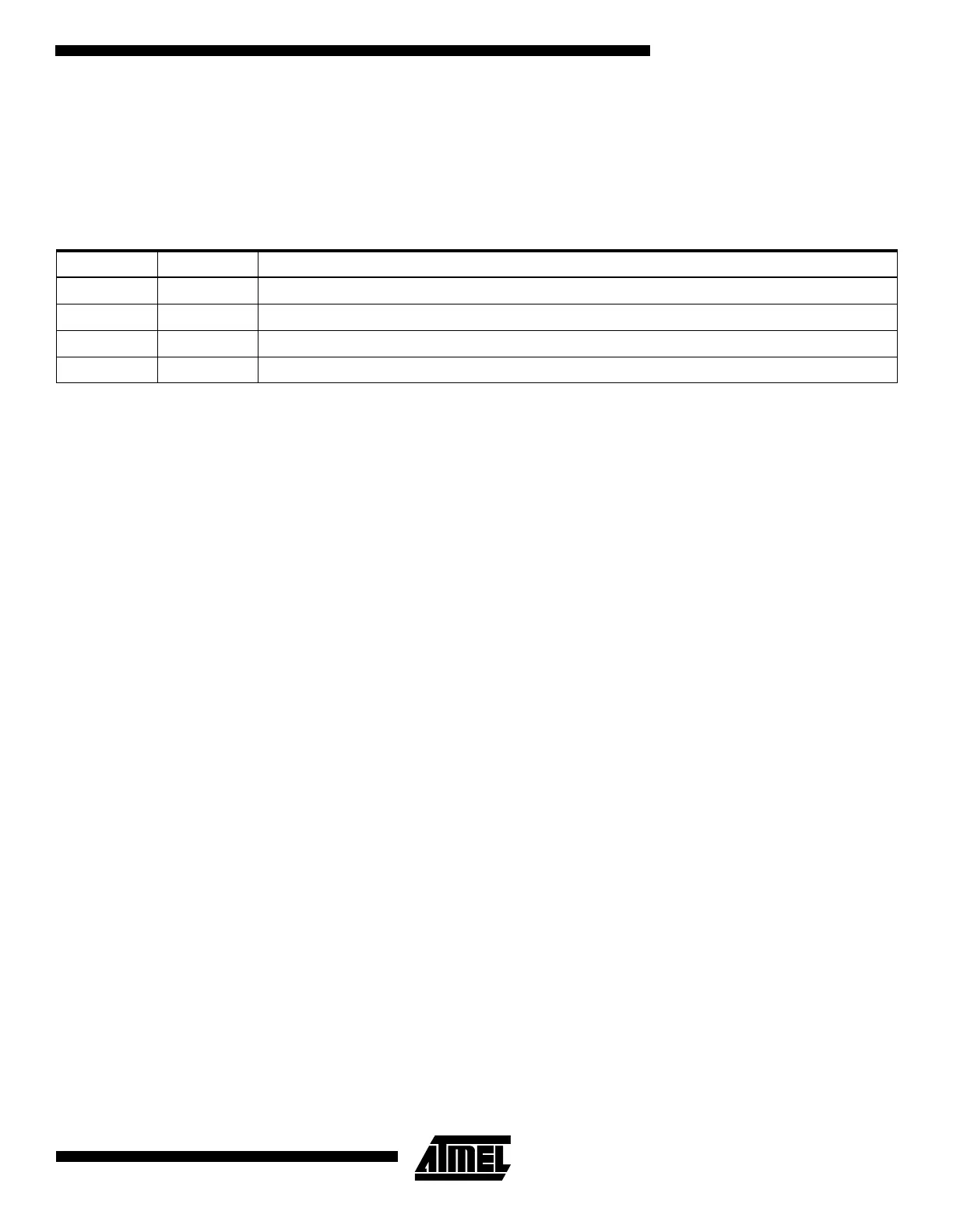

Table 13. Interrupt 0 Sense Control

ISC01 ISC00 Description

0 0 The low level of INT0 generates an interrupt request.

0 1 Any change on INT0 generates an interrupt request

1 0 The falling edge of INT0 generates an interrupt request.

1 1 The rising edge of INT0 generates an interrupt request.

Loading...

Loading...