10

ATtiny15L

1187H–AVR–09/07

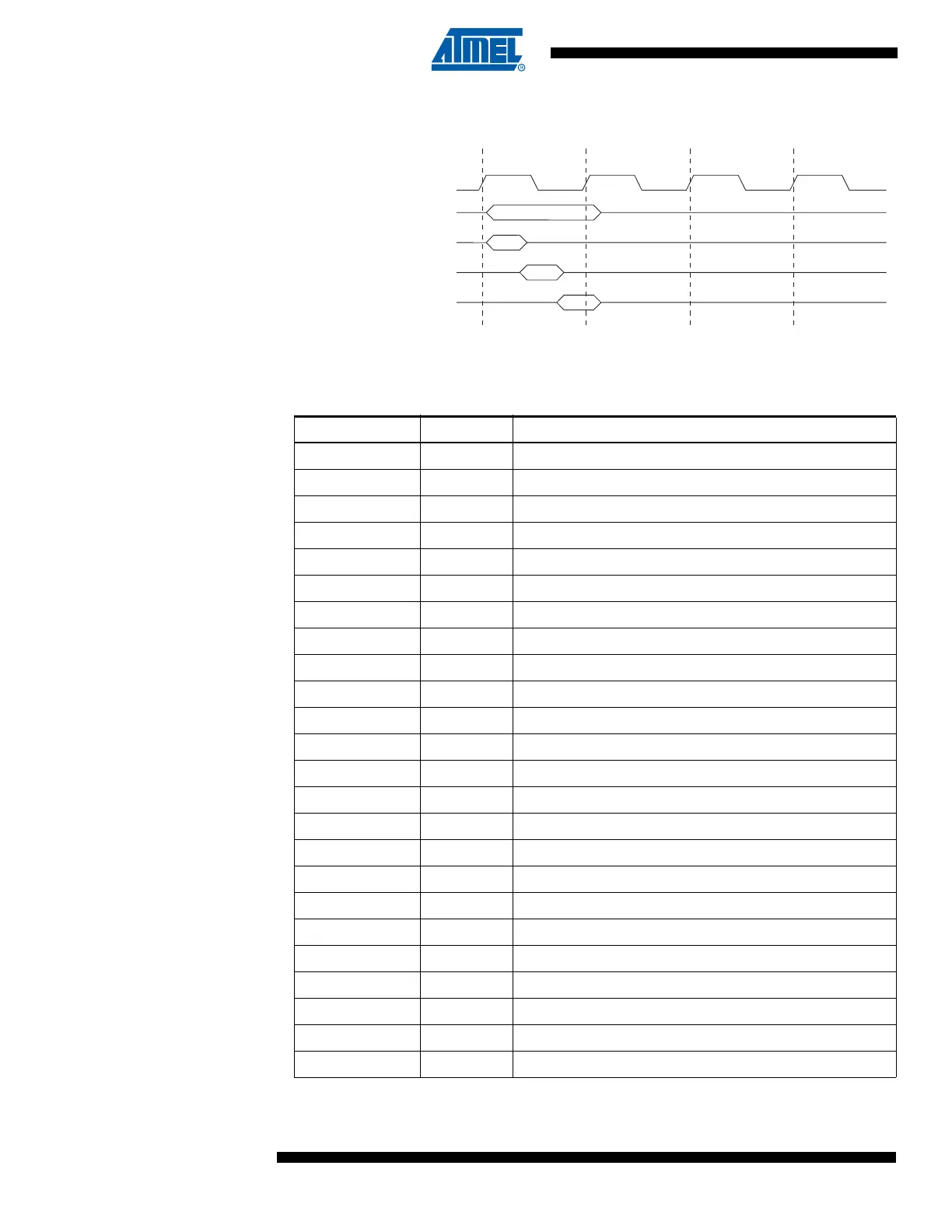

Figure 11. Single Cycle ALU Operation

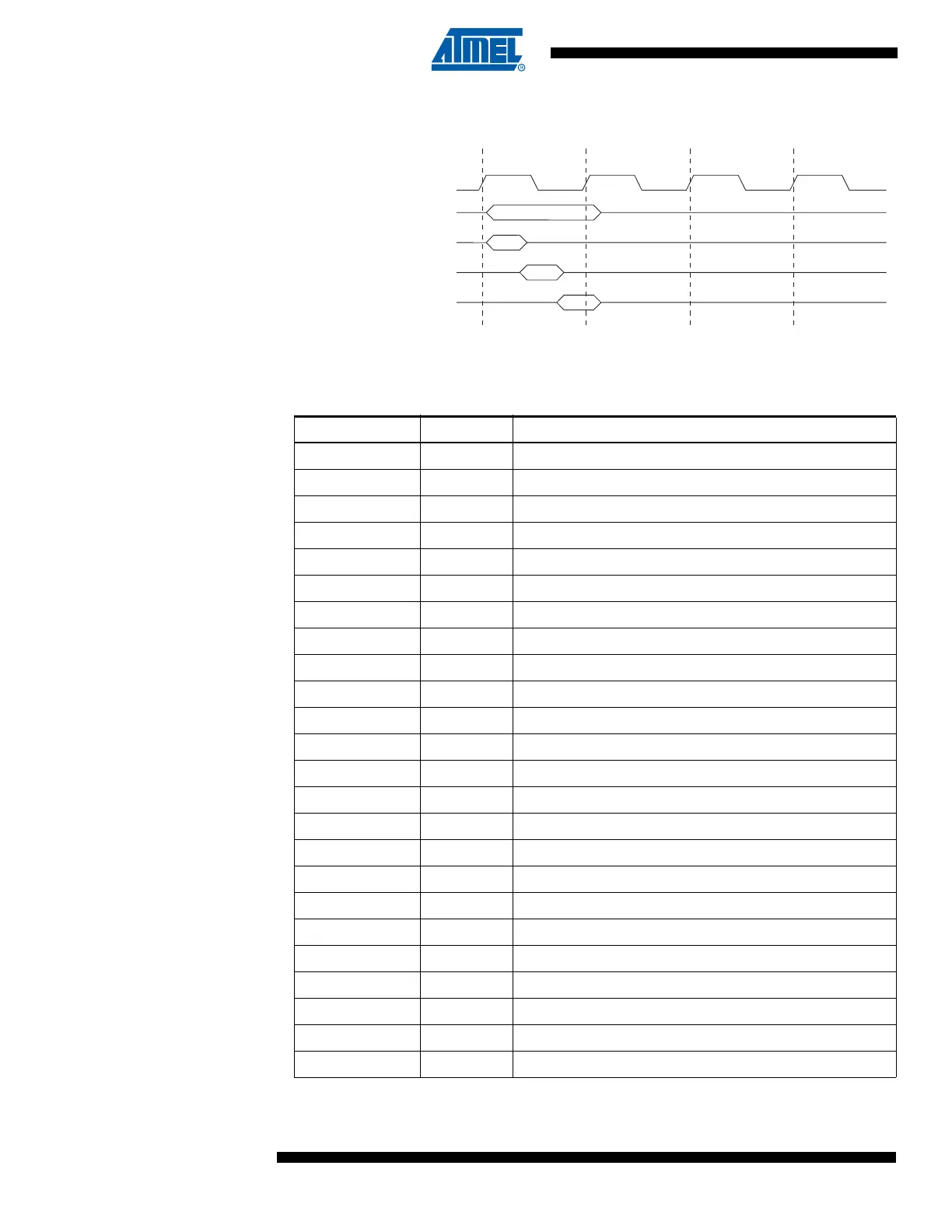

I/O Memory The I/O space definition of the ATtiny15L is shown in Table 2.

System Clock Ø

Total Execution Time

egister Operands Fetch

ALU Operation Execute

Result Write Back

T1 T2 T3 T4

Table 2. ATtiny15L I/O Space

(1)

Address Hex Name Function

$3F SREG Status Register

$3B GIMSK General Interrupt Mask Register

$3A GIFR General Interrupt Flag Register

$39 TIMSK Timer/Counter Interrupt Mask Register

$38 TIFR Timer/Counter Interrupt Flag Register

$35 MCUCR MCU Control Register

$34 MCUSR MCU Status Register

$33 TCCR0 Timer/Counter0 Control Register

$32 TCNT0 Timer/Counter0 (8-bit)

$31 OSCCAL Oscillator Calibration Register

$30 TCCR1 Timer/Counter1 Control Register

$2F TCNT1 Timer/Counter1 (8-bit)

$2E OCR1A Timer/Counter1 Output Compare Register A

$2D OCR1B Timer/Counter1 Output Compare Register B

$2C SFIOR Special Function I/O Register

$21 WDTCR Watchdog Timer Control Register

$1E EEAR EEPROM Address Register

$1D EEDR EEPROM Data Register

$1C EECR EEPROM Control Register

$18 PORTB Data Register, Port B

$17 DDRB Data Direction Register, Port B

$16 PINB Input Pins, Port B

$08 ACSR Analog Comparator Control and Status Register

$07 ADMUX ADC Multiplexer Select Register

Loading...

Loading...