52

ATtiny15L

1187H–AVR–09/07

The Port B Input Pins Address

– PINB

The Port B Input Pins address (PINB) is not a register, and this address enables access

to the physical value on each Port B pin. When reading PORTB, the PORTB Data Latch

is read, and when reading PINB, the logical values present on the pins are read.

PORT B as General Digital I/O The lower five pins in Port B are equal when used as digital I/O pins.

PBn, general I/O pin: The DDBn bit in the DDRB Register selects the direction of this

pin. If DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero),

PBn is configured as an input pin. If PORTBn is set (one) when the pin is configured as

an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the

PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. Pull-

ups for all ports can be disabled also by setting PUD-bit in the MCUCR Register.

Note: 1. n: 4, 3…0, pin number.

On ATtiny15L, PB5 is input or open-drain output. Because this pin is used for 12V pro-

gramming, there is no ESD protection diode limiting the voltage on the pin to

V

CC

+ 0.5V. Thus, special care should be taken to ensure that the voltage on this pin

does not rise above V

CC

+ 1V during normal operation. This may cause the MCU to

reset or enter Programming mode unintentionally.

All Port B pins are connected to a pin change detector that can trigger the pin change

interrupt. See “Pin Change Interrupt” on page 22 for details.

Alternate Functions of Port B The alternate pin functions of Port B are:

• RESET

– PORT B, Bit 5

When the RSTDISBL Fuse is unprogrammed, this pin serves as External Reset. When

the RSTDISBL Fuse is programmed, this pin is a general input pin or a open-drain out-

put pin. If DDB5 is cleared (zero), PB5 is configured as an input pin. If DDB5 is set

(one), the pin is a open-drain output.

• SCK/INT0/T0 – PORT B, Bit 2

In Serial Programming mode, this pin serves as the serial clock input, SCK.

In Normal mode, this pin can serve as the external interrupt0 input. See the interrupt

description for details on how to enable this interrupt. Note that activity on this pin will

trigger the interrupt even if the pin is configured as an output.

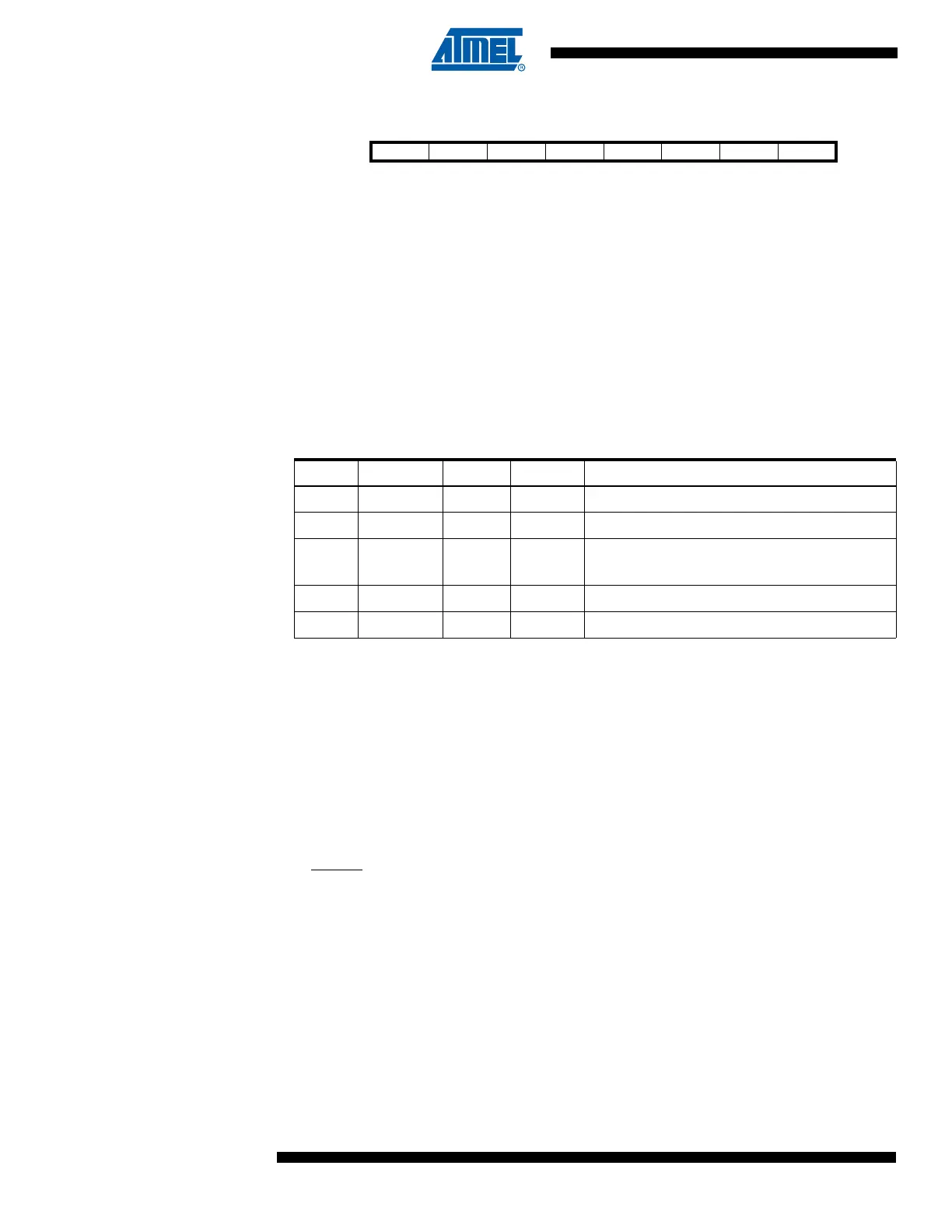

Bit 76543210

$16 – – PINB5 PINB4 PINB3 PINB2 PINB1 PINB0 PINB

Read/WriteRRRRRRRR

Initial Value 0 0 N/A N/A N/A N/A N/A N/A

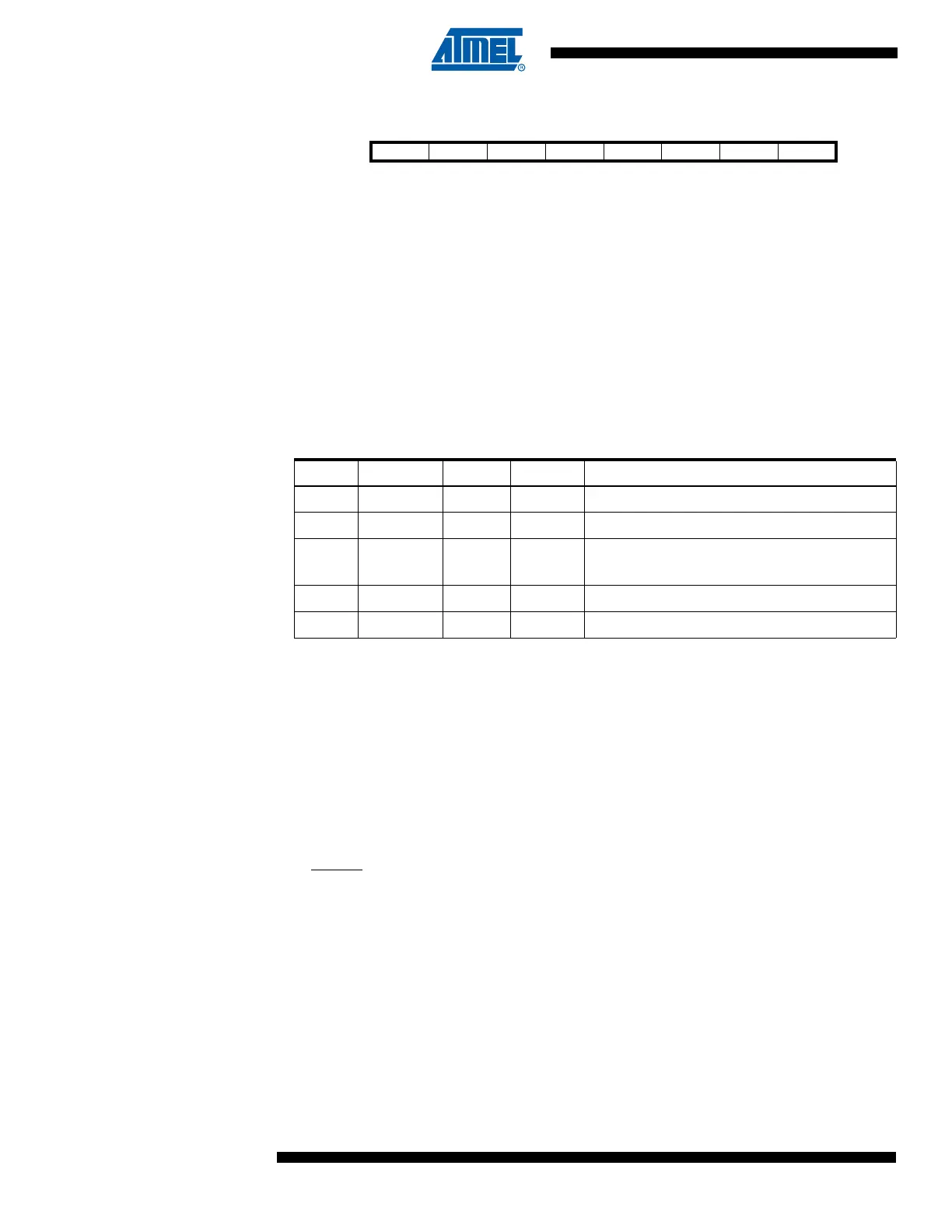

Table 22. DDBn Effects on Port B Pins

(1)

DDBn PORTBn I/O Pull-up Comment

0 0 Input No Tri-state (High-Z)

0 1 Input No PUD bit in the MCUCR Register is set.

0 1 Input Yes

PBn will source current if ext. pulled low.

PUD bit in the MCUCR Register is cleared.

1 0 Output No Push-pull Zero Output

1 1 Output No Push-pull One Output

Loading...

Loading...