3-Feb-2015

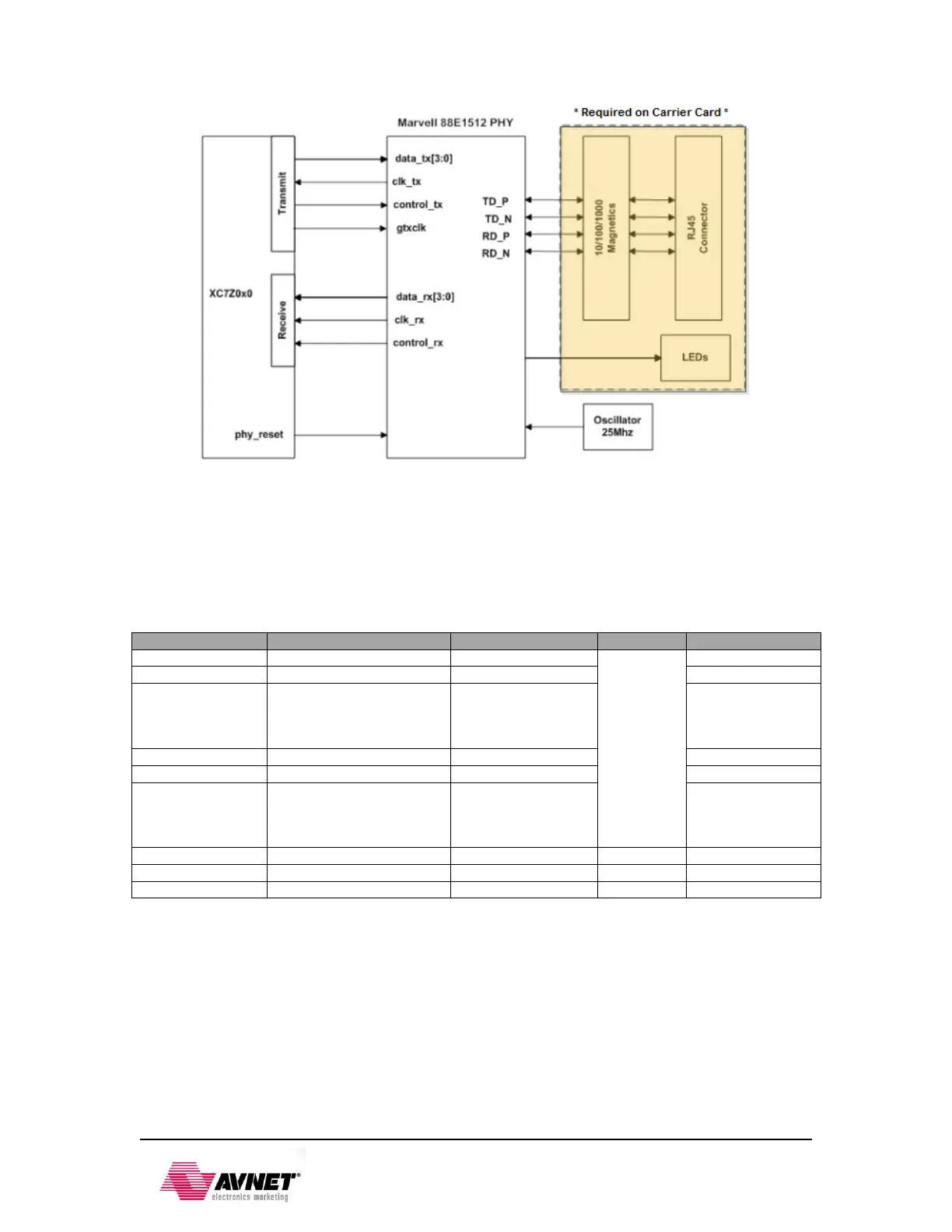

Figure 3 – 10/100/1000 Ethernet Interface

Zynq requires a voltage reference for RGMII interfaces. Thus PS_MIO_VREF, E11, is tied to

0.9V, half the bank voltage of MIO Bank 1/501. The 0.9V is generated through a resistor divider.

The 88E1512 also requires a 25 MHz input clock. An ABRACON ASDMB-25.000MHZ-LC-T is

used as this reference.

Table 6 – Ethernet PHY Pin Assignment and Definitions

RXD0: D11

RXD1: A16

RXD2: F15

RXD3: A15

TXD0: E14

TXD1: B18

TXD2: D10

TXD3: A17

** Requires a resistor change to the board to use PHY Reset. By default MIO47 is routed to JX3.

The datasheet for the Marvell 88E1512 is not available publicly. An NDA is required for this

information. Please contact your local Avnet or Marvell representative for assistance.

Loading...

Loading...