Camera Link Implementation AW00118702000

20 Basler racer Camera Link

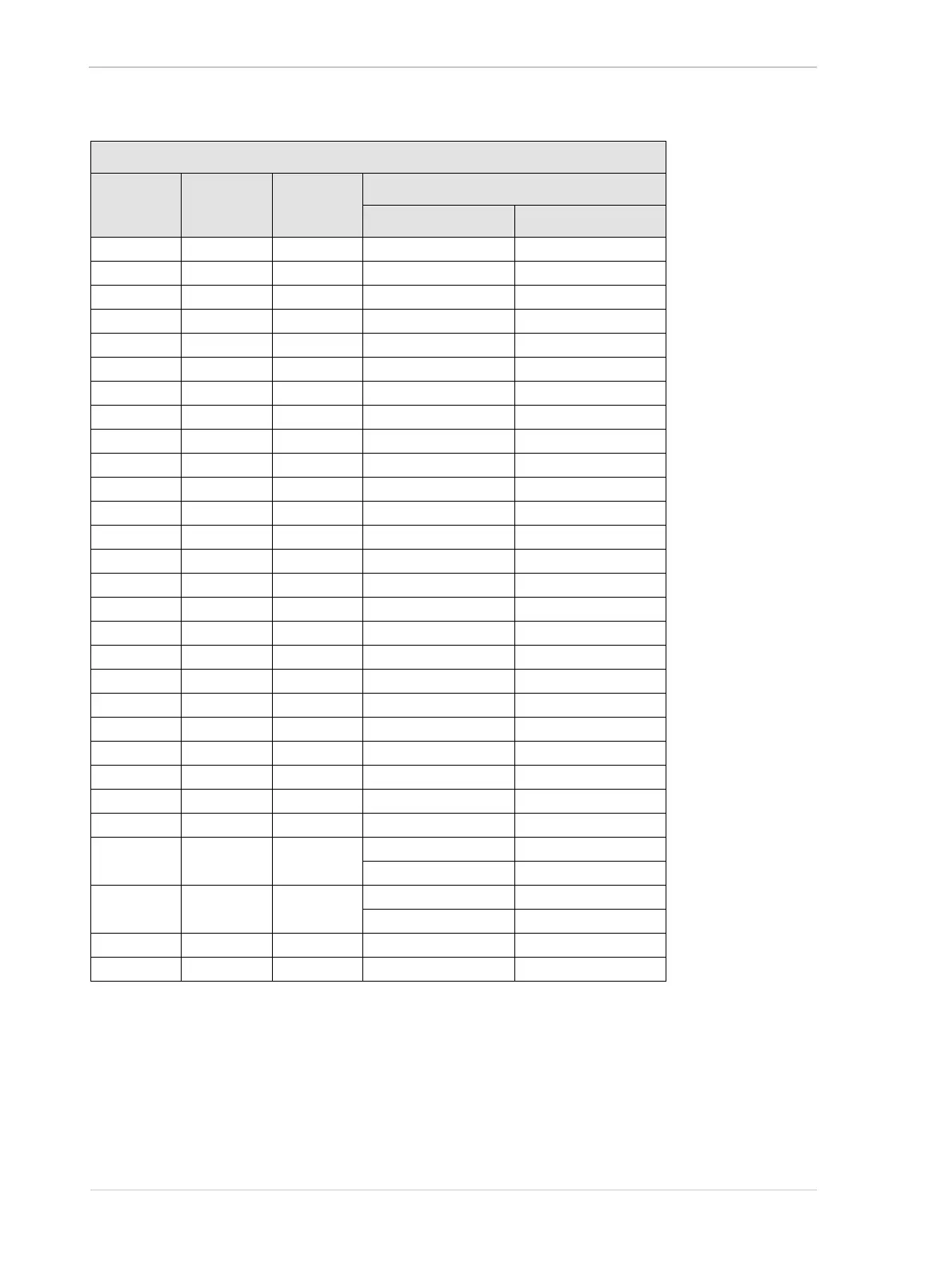

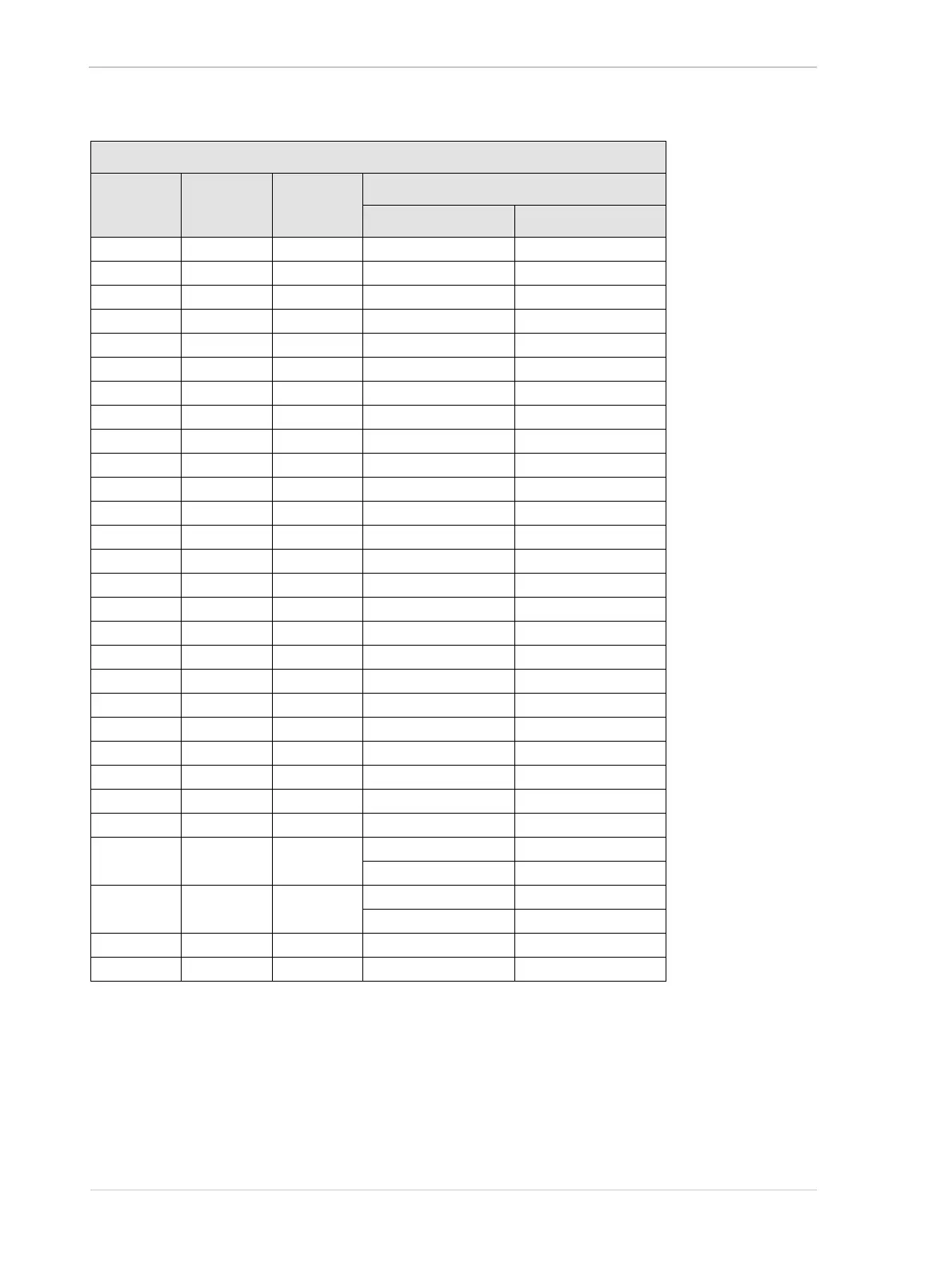

* In 1X8 8 bit mode, this port is FVAL and is not used.

In 1X8 10 bit mode, FVAL is not present. Instead, this port is J5 and D6 Bit 1 is assigned to it.

** In 1X8 8 bit mode, this port is DVAL.

In 1X8 10 bit mode, DVAL is not present. Instead, this port is J6 and D7 Bit 0 is assigned to it.

Medium/Full SDR Conn, Transmitter Circuit Z

Port Camera Frame

Grabber

Bit Assignments

1X8 - 8 Bits 1X8 - 10 Bits

Port G0 TxIn0 RxOut0 D6 Bit 0 D6 Bit 2

Port G1 TxIn1 RxOut1 D6 Bit 1 D6 Bit 3

Port G2 TxIn2 RxOut2 D6 Bit 2 D6 Bit 4

Port G3 TxIn3 RxOut3 D6 Bit 3 D6 Bit 5

Port G4 TxIn4 RxOut4 D6 Bit 4 D6 Bit 6

Port G5 TxIn6 RxOut6 D6 Bit 5 D6 Bit 7

Port G6 TxIn27 RxOut27 D6 Bit 6 D6 Bit 8

Port G7 TxIn5 RxOut5 D6 Bit 7 (MSB) D6 Bit 9 (MSB)

Port H0 TxIn7 RxOut7 D7 Bit 0 D7 Bit 2

Port H1 TxIn8 RxOut8 D7 Bit 1 D7 Bit 3

Port H2 TxIn9 RxOut9 D7 Bit 2 D7 Bit 4

Port H3 TxIn12 RxOut12 D7 Bit 3 D7 Bit 5

Port H4 TxIn13 RxOut13 D7 Bit 4 D7 Bit 6

Port H5 TxIn14 RxOut14 D7 Bit 5 D7 Bit 7

Port H6 TxIn10 RxOut10 D7 Bit 6 D7 Bit 8

Port H7 TxIn11 RxOut11 D7 Bit 7 (MSB) D7 Bit 9 (MSB)

Port I5 TxIn15 RxOut15 Not Used D2 Bit 1

Port I6 TxIn18 RxOut18 Not Used D3 Bit 0

Port I7 TxIn19 RxOut19 Not Used D3 Bit 1

Port J0 TxIn20 RxOut20 Not Used D4 Bit 0

Port J1 TxIn21 RxOut21 Not Used D4 Bit 1

Port J2 TxIn22 RxOut22 Not Used D5 Bit 0

Port J3 TxIn16 RxOut16 Not Used D5 Bit 1

Port J4 TxIn17 RxOut17 Not Used D6 Bit 0

LVAL TxIn24 RxOut24 Line Valid Line Valid

FVAL or

Port J5 *

TxIn25 RxOut25 Not Used

D6 Bit 1

DVAL or

Port J6 **

TxIn26 RxOut26 Not Used

D7 Bit 0

Port J7 TxIn23 RxOut23 Not Used D7 Bit 1

Strobe TxInCLK RxOutClk Pixel Clock Pixel Clock

Table 10: Bit Assignments for 1X8 Tap Geometry – 8 or 10 Bit Pixel Depth (Transmitter Circuit Z)

Loading...

Loading...