5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

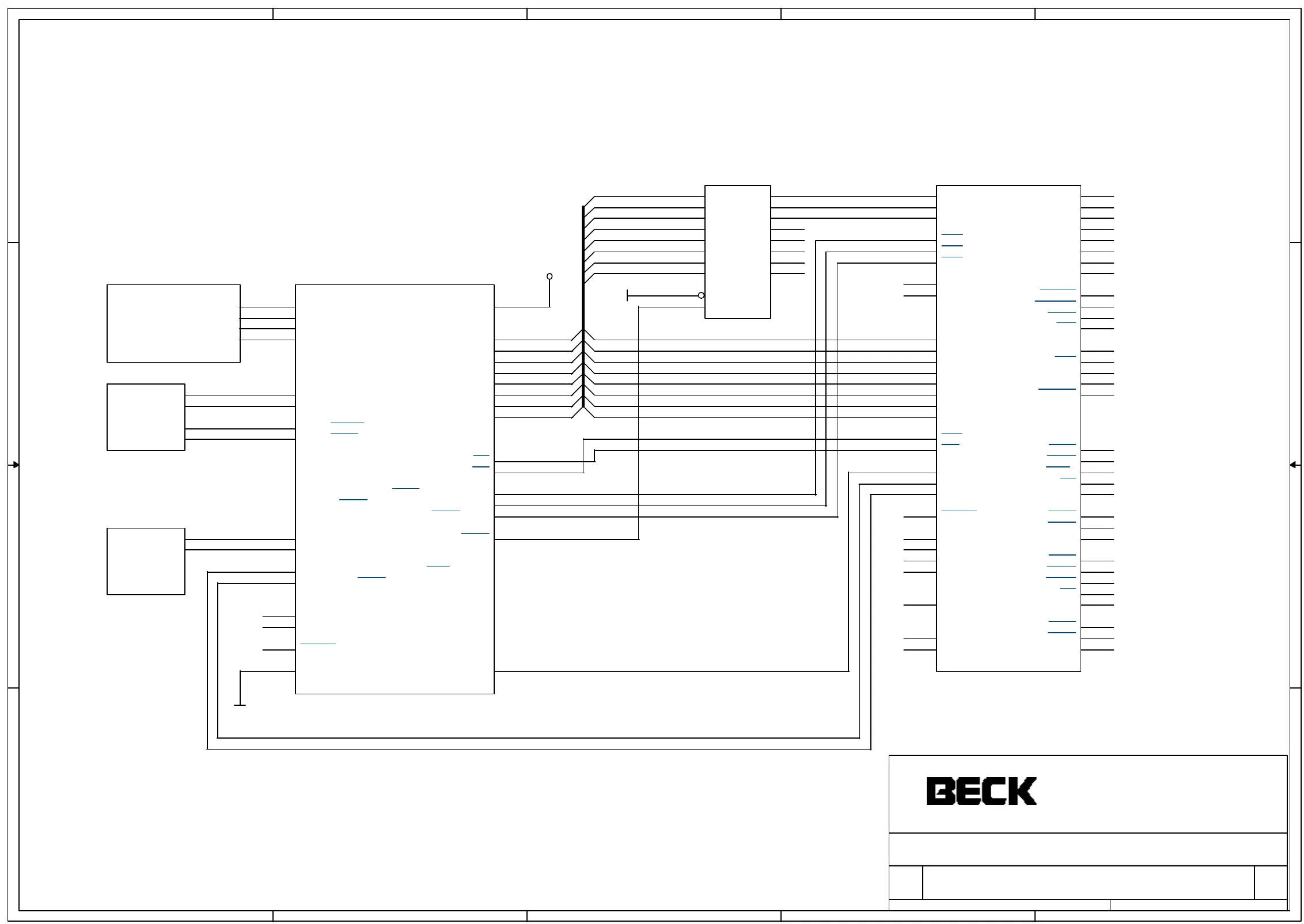

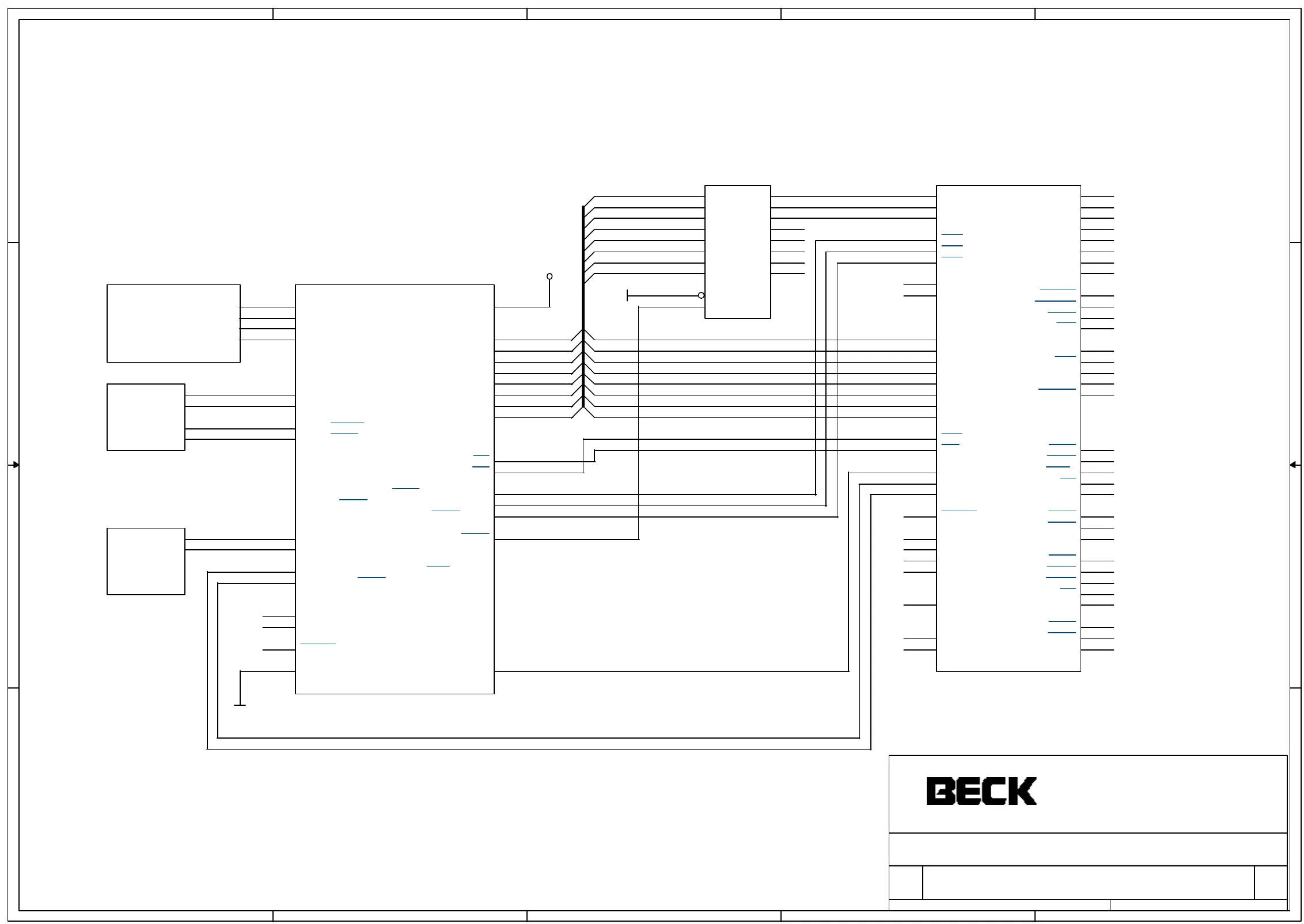

EXT1 10BaseTEXT0

16C452/552 2 UART with FIFO

and Printer Port

(c) 1996 - 99 CHIP D1

0.5

IPC@CHIP SC12 circuit example

IPC GmbH

Germany - 35578 Wetzlar

Garbenheimer Stra sse 38

A4

1 1Tuesday, November 23, 1999

Title

Size Document Num ber Rev

Date: Sheet of

INT0

INT4

INT4

INT2

INT2

INT0

AD4

AD6

AD3

A2

A0

AD3

AD1

WR#

AD6

PCS5#

A1

AD6

AD5

PCS6#

AD5

AD0

AD5

AD3

AD1

PCS1#

AD7

AD4

AD0

AD1

AD4

AD2

AD7

AD2

AD0

AD2

AD7

RD#

ALE

ALE

GND

VCC

GND

IC3

74HCT 373

3

4

7

8

13

14

17

18

1

11

2

5

6

9

12

15

16

19

D0

D1

D2

D3

D4

D5

D6

D7

OC

G

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

IC2

16C452/552

35

34

33

14

15

16

17

18

19

20

21

32

3

38

44

36

37

45

60

59

39

4

1

53

52

51

50

49

48

47

46

55

56

58

57

66

68

67

65

63

28

31

29

30

41

24

25

26

13

5

8

6

62

12

11

10

2

9

22

42

43

61

A0

A1

A2

D0

D1

D2

D3

D4

D5

D6

D7

CS0

CS1

CS2

BD0

IOW

IOR

INT0

INT1

INT2

RESET

CLK

LPTOE

P0

P1

P2

P3

P4

P5

P6

P7

STROB

AUTOFD

SLCT

INIT

BUSY

ACK

PE

SLCT

ERROR

CTS1

DSR1

DCD1

RI1

SIN1

RTS1

DTR1

SOUT1

CTS2

DSR2

DCD2

RI2

SIN2

RTS2

DTR2

SOUT2

TRI

RXRDY0#

TXRDY0#

TXRDY1#

ENIRQ

RXRDY1#

IC1

IPC@CHIP SC12

8

9

10

11

12

13

14

15

22

23

27

28

29

24

18

19

20

21

2

1

3

4

5

6

25

26

31

30

17

16 7

32

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

RD

WR

MCS0/PCS1/P4/TMRIN0/A0

PCS5/P3/TMROUT1/TMRIN1/A1

PCS6/P2/A2

ALE/PCS0

TPTX+

TPTX-

TPRX+

TPRX-

TXD0/P8

RXD0/P7

CTS0/ENRX0/P9

RTS0/RTR0/P10

TXD1/P11

RXD1/INT3/P12

CTS1/MEN/PCS2/P6/INT2/INTA/PW

RTS1/MOSI/PCS3/P5/INT4

I2CCLK/MSCK/DRQ1/INT6/P0

I2CDAT/MISO/DRQ0/INT5/P1

RESET_PFAIL_LILED

GND TMROUT0/INT0/P13

VCC

Loading...

Loading...