5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

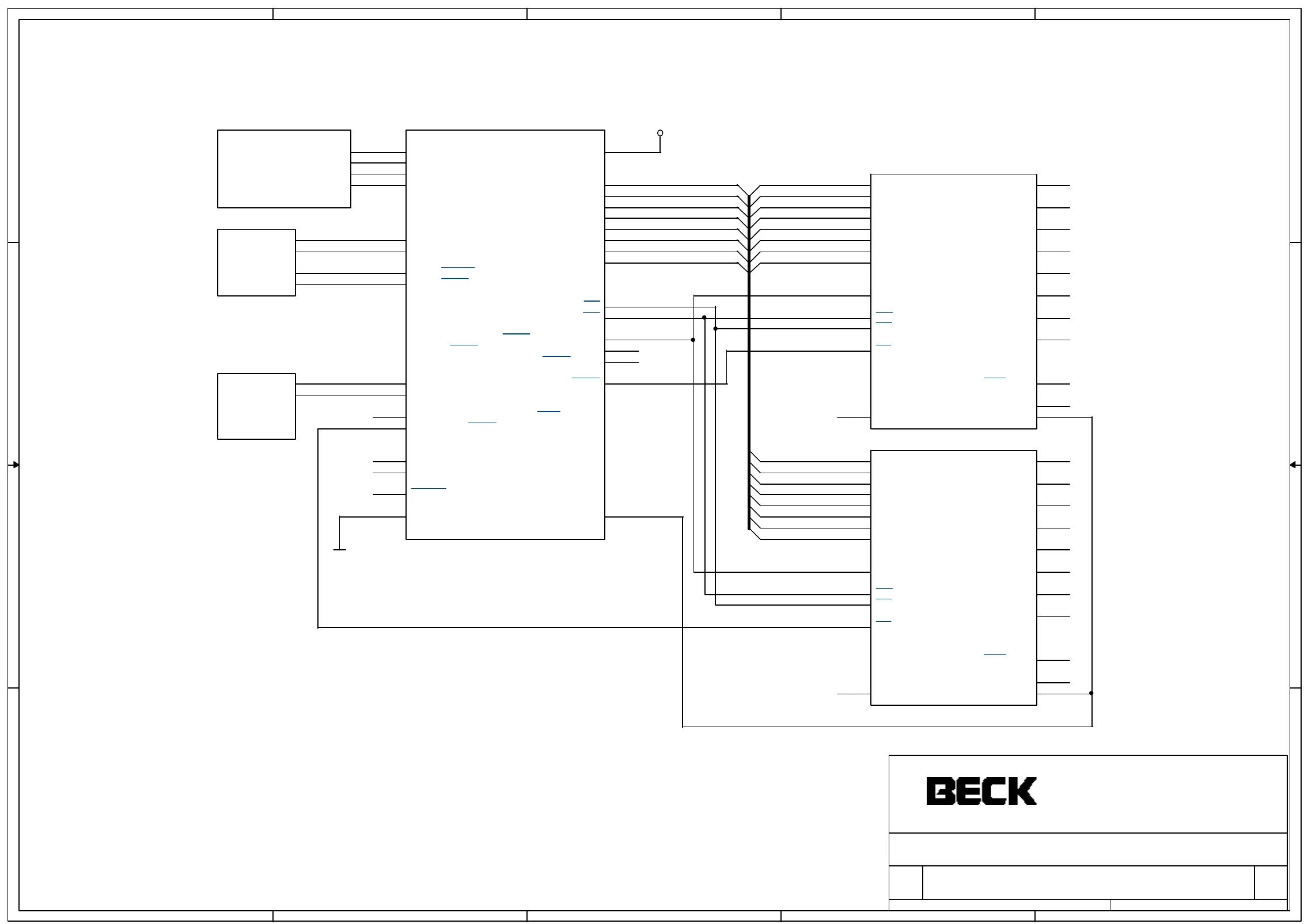

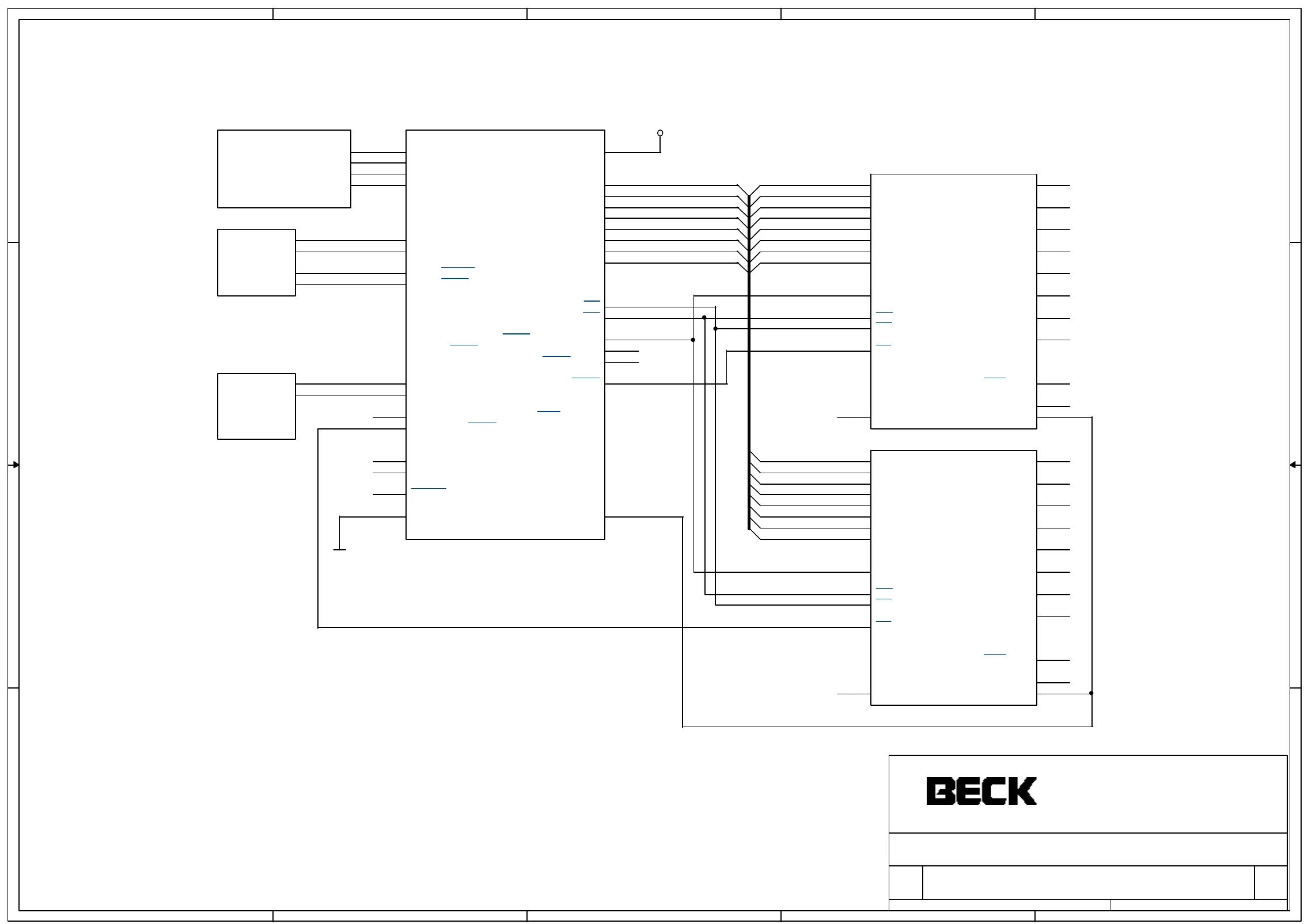

EXT1 10BaseTEXT0

16x 10bit ADC with 2x µPD7004

(c) 1996 - 99 CHIP D1

0.5

IPC@CHIP SC12 circuit example

IPC GmbH

Germany - 35578 Wetzlar

Garbenheimer Stra sse 38

A4

1 1Tuesday, November 23, 1999

Title

Size Document Num ber Rev

Date: Sheet of

WR#

AD7

AD5

AD4

AD1

RD#

AD3

AD0

AD2

RD#

AD2

TMROUT0

WR#

AD6

AD0

AD5

AD1

AD4

AD6

AD7

AD3

AD7

AD1

AD2

AD0

AD5

AD6

AD4

AD3

RD#

A0

A0

A0

PCS0#

PCS0#

PCS3#

WR#

PCS3#

GND

VCC

IC2

UPD70 04

25

26

27

28

1

2

3

4

17

18

14

13

12

11

10

9

8

7

20

19

21

22

16

5

ACH0

ACH1

ACH2

ACH3

ACH4

ACH5

ACH6

ACH7

CLKIN

MODE

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

A0

WR

RD

CS

EOC OUT

V REF

IC3

UPD70 04

25

26

27

28

1

2

3

4

17

18

14

13

12

11

10

9

8

7

20

19

21

22

16

5

ACH0

ACH1

ACH2

ACH3

ACH4

ACH5

ACH6

ACH7

CLKIN

MODE

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

A0

WR

RD

CS

EOC OUT

V REF

IC1

IPC@CHIP SC12

8

9

10

11

12

13

14

15

22

23

27

28

29

24

18

19

20

21

2

1

3

4

5

6

25

26

31

30

17

16 7

32

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

RD

WR

MCS0/PCS1/P4/TMRIN0/A0

PCS5/P3/TMROUT1/TMRIN1/A1

PCS6/P2/A2

ALE/PCS0

TPTX+

TPTX-

TPRX+

TPRX-

TXD0/P8

RXD0/P7

CTS0/ENRX0/P9

RTS0/RTR0/P10

TXD1/P11

RXD1/INT3/P12

CTS1/MEN/PCS2/P6/INT2/INTA/PW

RTS1/MOSI/PCS3/P5/INT4

I2CCLK/MSCK/DRQ1/INT6/P0

I2CDAT/MISO/DRQ0/INT5/P1

RESET_PFAIL_LILED

GND TMROUT0/INT0/P13

VCC

Loading...

Loading...