5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

To eDP Panel CONN

DIFF=100ohm

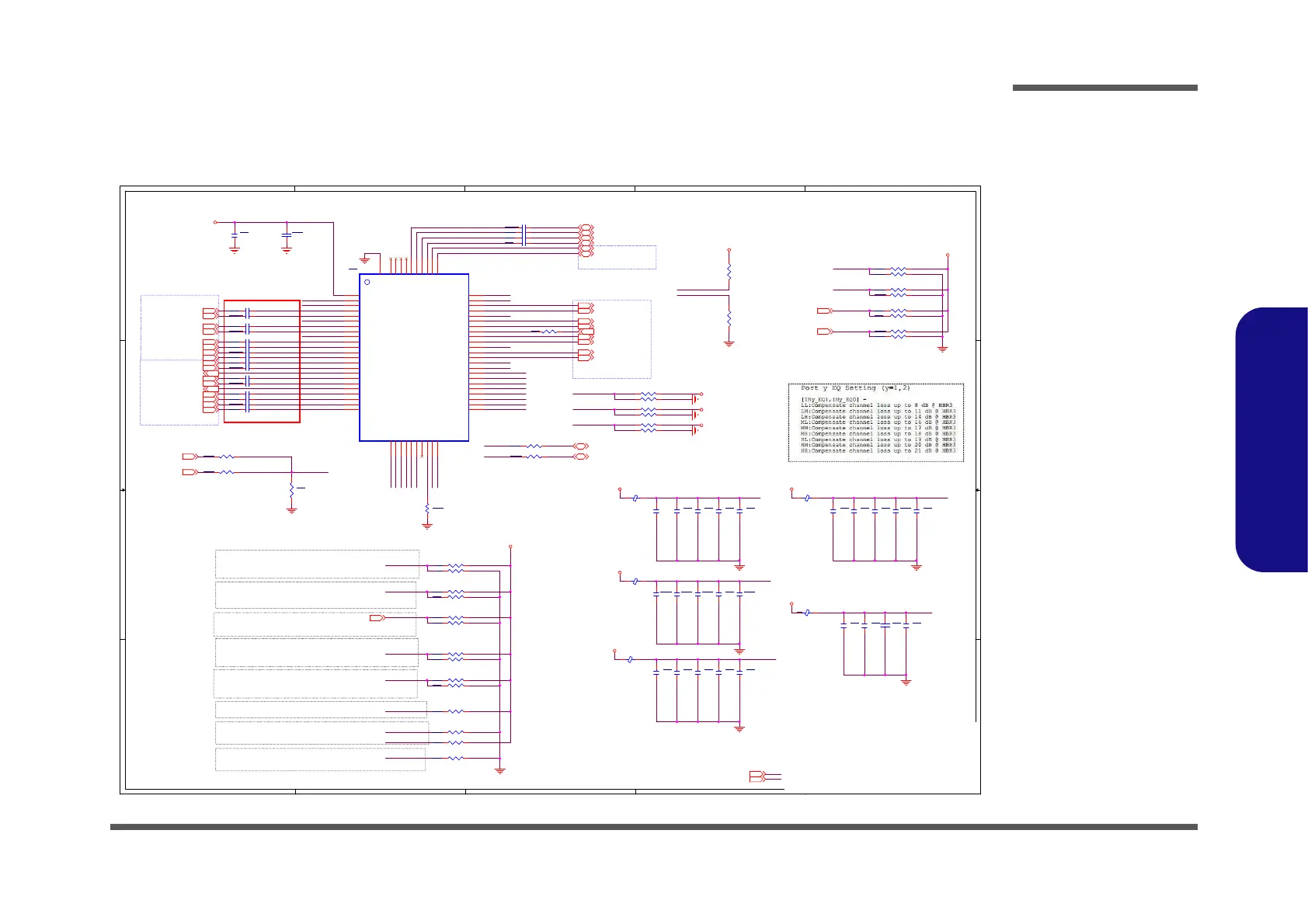

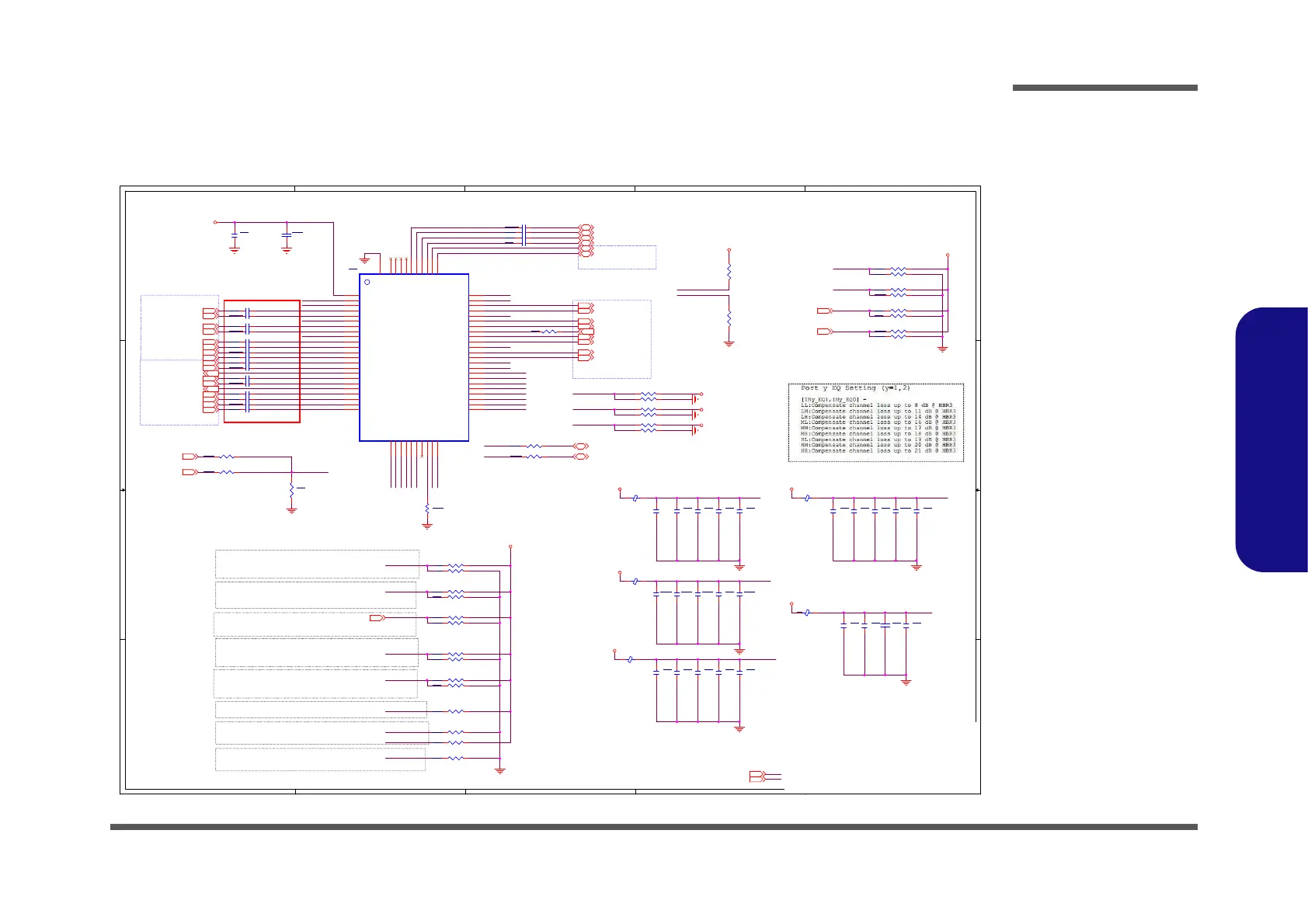

CFG0 Operation mode configuration for Input port#1:

L:DP Port is configured to Auto jitter cleaning mode

(default)

M:DP Port is configured to Redriving mode

H:DP Port is configured to Full jitter cleaning mode

SW=

L: Port1 is selected as the input port

H: Port2 is selected as the input port

I2C_ADDR =

L:Default I2C address, 0x10-0x2F

H:Alternative I2C address, 0x90-0x9F and

0xD0-0xDF

CFG4 Operation mode configuration for Input port#2:

L:DP Port is configured to Auto jitter cleaning mode

(default)

M:DP Port is configured to Redriving mode

H:DP Port is configured to Full jitter cleaning mode

Auto EQ option for Input Port1

CFG1 =

L:Auto EQ enabled (default)

EQ automatically adjusted based on link training.

H:Auto EQ disabled.

Auto EQ option for Input Port2

CFG3 =

L:Auto EQ enabled (default)

EQ automatically adjusted based on link training.

H:Auto EQ disabled.

CFG2 Output Configuration

ϗ

L: DP output is dynamic adjusted based on link training (default)

M: DP output is fixed to 400mV/0dB

H: DP output is fixed to 800mV/3.5dB

VDD_DDC: DDC Passive Switch Supply Power.

It should be connected with 1.8V or 3.3V

which depends on the DDC IO voltage of source IC

FROM PCH (GPP_F9)

HIGH=PS8331B PORT2 (dGPU)

LOW=PS8331B PORT1 (iGPU) (DEFAULT)

FROM DDS FUNCTION

From Nvidia

Frome Intel

CAP NEAR PS8461DIFF=85ohm

DIFF=90ohm

From Nvidia

DIFF=90ohm

Frome Intel

DIFF=85ohm

To eDP Panel CONN

EQ CHECK

2021/08/19

DEDP_D_AUX_SCL_R

DEDP_D_AUX#_SDA_R

IEDP_AUX#_R

IEDP_AUX_R

DP1_SW1_REXT

EDP_HPD_R

SW1_IN1_EQ1

SW1_IN1_EQ0

SW1_IN2_EQ1

SW1_IN2_EQ0

SW1_CFG3

SW1_CFG0

SW1_CFG1

SW1_CFG2

SW1_CFG4

SW1_EDP_AUXP

I2C_ADDR_SW1

SW1_IN1_EQ0

SW1_IN2_EQ1

SW1_IN2_EQ0

SW1_IN1_EQ1

SW1_EDP_AUXN

MID1_CA_DET

MID1_CA_DET

VDD33_A

VDD33_A

VDD12_A

VDDA12_A

VDDRX12_A

VDDRX12_A

VDDTX12_A

VDDTX12_A

VDD33_AVDD12_A

VDDRX12_A

IEDP_TXP_0_R

IEDP_TXN_0_R

VDDTX12_A

VDDA12_A

IEDP_TXP_1_R

IEDP_TXN_1_R

IEDP_TXP_2_R

IEDP_TXN_2_R

I2C_ADDR_SW1

EDP_SW_R

IEDP_TXP_3_R

IEDP_TXN_3_R

DEDP_D0_R

DEDP_D#0_R

DEDP_D1_R

DEDP_D#1_R

DEDP_D2_R

DEDP_D#2_R

DEDP_D3_R

DEDP_D#3_R

EDP_SW_R

SW1_CFG3

SW1_CFG2

SW1_CFG1

SW1_CFG0

SW1_CFG4

VDD12_A

CSDA

CSCL

CSCL

CSDA

SW1_EDP_AUXN

SW1_EDP_AUXP

RSV0 RSV0

RSV1

RSV2

RSV1

RSV2

3.3VS

3.3VS

3.3VS

3.3VS1.2VS

1.2VS

1.2VS

1.2VS

3.3VS

3.3VS

3.3VS

3.3VS

CPU_EDP_AUXN 4

CPU_EDP_AUXP 4

DEDP_D_AUX_SCL 35

DEDP_D_AUX#_SDA 35

EDP_HPD_R_R 17

DP_TXN0 17

DP_TXP0 17

DP_TXN1 17

DP_TXP1 17

DP_TXP2 17

DP_TXN2 17

DP_TXP3 17

DP_TXN3 17

PS8461_SW10

CPU_EDP_TXP04

CPU_EDP_TXN04

CPU_EDP_TXP14

CPU_EDP_TXN14

CPU_EDP_TXP24

CPU_EDP_TXN24

CPU_EDP_TXP34

CPU_EDP_TXN34

DEDP_D035

DEDP_D#035

EDP_HPD4

DEDP_D135

DEDP_D#135

IN2_HPD35

PS8461_SW_R39

DEDP_D235

DEDP_D#235

DEDP_D335

DEDP_D#335

SW1_EDP_AUXP 17

SW1_EDP_AUXN 17

SMC_BAT 32,52,63,67,74

SMD_BAT 32,52,63,67,74

SW1_IN1_EQ052

SW1_IN1_EQ152

SW1_CFG252

3.3VS4,5,6,8,10,11,15,16,17,19,32,39,43,44,46,48,51,53,54,56,57,59,60,63,66,74

1.2VS69

Title

Size Document Number Re v

Date: Sheet

of

6-71-PD500-D02

D02

[42] eDP 2-TO-1 PS8461 SW

A3

42 83Friday, February 18, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

PDxxPNP_PNN_PNT

Title

Size Document Number Re v

Date: Sheet

of

6-71-PD500-D02

D02

[42] eDP 2-TO-1 PS8461 SW

A3

42 83Friday, February 18, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

PDxxPNP_PNN_PNT

Title

Size Document Number Re v

Date: Sheet

of

6-71-PD500-D02

D02

[42] eDP 2-TO-1 PS8461 SW

A3

42 83Friday, February 18, 2022

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

PDxxPNP_PNN_PNT

R736 *4.7K_04

C1094 0.22u_10V_X5R_02

C105

0.1u_16V_X5R_02

.

L9 HCB1608KF-121T30

R730

100K_04

MUX PS8461

R70 *4.7K_04

C1097 0.22u_10V_X5R_02

R738 4.7K_04

R66 4.7K_04

C113

0.01u_50V_X7R_04

C75

0.01u_50V_X7R_04

R50 *4.7K_04

R740 4.7K_04

C1099 0.22u_10V_X5R_02

R735 4.7K_04

R110 4.7K_04

R751 *0_04

C111

1u_6.3V_X5R_04

C65

0.01u_50V_X7R_04

R104 0_04

MUX PS8461

C97

0.01u_50V_X7R_04

R737 4.7K_04

C95 0.1u_10V_X7R_04

C1108 0.22u_10V_X5R_02

C1106 0.22u_10V_X5R_02

C1107 0.22u_10V_X5R_02

R739 *4.7K_04

C80

0.01u_50V_X7R_04

U51

PS8461E

VDD_DDC

1

VDD33

2

VDDRX12

3

IN1_D0p

4

IN1_D0n

5

I2C_ADDR

6

IN1_D1p

7

IN1_D1n

8

SW

9

IN1_D2p

10

IN1_D2n

11

IN1_D3p

12

IN1_D3n

13

IN2_D0p

14

IN2_D0n

15

IN1_HPD

16

IN2_D1p

17

IN2_D1n

18

IN2_HPD

19

IN2_D2p

20

VDDRX12

24

CFG3

25

CFG2

26

CFG1

27

CFG0

28

VDD33

29

PD#

30

REXT

31

VDD12

32

CSDA

33

CSCL

34

RSV2

35

RSV1

36

RSV0

37

IN2_EQ0

38

IN2_EQ1

39

IN1_EQ0

40

IN1_EQ1

41

VDDTX12

42

VDDA12

43

OUT_D3n

44

OUT_D3p

45

CFG4

46

OUT_D2n

47

OUT_D2p

48

OUT_HPD

49

OUT_D1n

50

OUT_D1p

51

DP_CADET

52

OUT_D0n

53

OUT_D0p

54

VDDTX12

55

VDD12

56

DP_AUXn_SDA

57

DP_AUXp_SCL

58

IN2_AUXn

59

IN2_AUXp

60

IN1_AUXn

61

IN2_D2n

21

IN2_D3p

22

IN2_D3n

23

IN1_AUXp

62

IN2_SDA

63

EPAD

67

IN2_SCL

64

IN1_SCL

66

IN1_SDA

65

R745 *4.7K_04

C89

4.7u_6.3V_X5R_04

R51 0_04

C100

0.1u_16V_X5R_02

R726 4.7K_04

C1092 0.1u_10V_X7R_04

C84

0.1u_16V_X5R_02

C102

4.7u_6.3V_X5R_04

C85

0.1u_16V_X5R_02

.

L6 HCB1608KF-121T30

C1098 0.22u_10V_X5R_02

C70

4.7u_6.3V_X5R_04

C64

0.1u_16V_X5R_02

R743 *4.7K_04

C1101 0.22u_10V_X5R_02

.

L7 HCB1608KF-121T30

R111 *4.7K_04

C1110 0.22u_10V_X5R_02

R729

100K_04

MUX PS8461

R81 4.7K_04

R93

100K_04

R65 *4.7K_04C1093 0.22u_10V_X5R_02

.

L5 HCB1608KF-121T30

R756

4.99K_1%_04

R102 4.7K_04

R100 *0_04

MUX PS8461

R61 4.7K_04

C71

0.1u_16V_X5R_02

.

L8 HCB1608KF-121T30

C67

0.01u_50V_X7R_04

R109 *4.7K_04

C93

0.01u_50V_X7R_04

R92 *4.7K_04

C63

0.1u_16V_X5R_02

R747 *0_04

C96 0.1u_10V_X7R_04

C94

0.1u_10V_X5R_04

C1105 0.22u_10V_X5R_02

C68

0.01u_50V_X7R_04

R707 *100K_04

R60 1M_04

C49

1u_6.3V_X5R_04

C66

0.1u_16V_X5R_02

R742 4.7K_04

C1091 0.1u_10V_X7R_04

C90

0.1u_16V_X5R_02

C101

0.01u_50V_X7R_04

C1095 0.22u_10V_X5R_02

R746 *4.7K_04

R103 4.7K_04

R706 *100K_04

R741 4.7K_04

C50

4.7u_6.3V_X5R_04

C1096 0.22u_10V_X5R_02

C1102 0.22u_10V_X5R_02

C1100 0.22u_10V_X5R_02

C98

4.7u_6.3V_X5R_04

C1109 0.22u_10V_X5R_02

R112 4.7K_04

Loading...

Loading...