27

AVR-3803/1083/AVC-3570

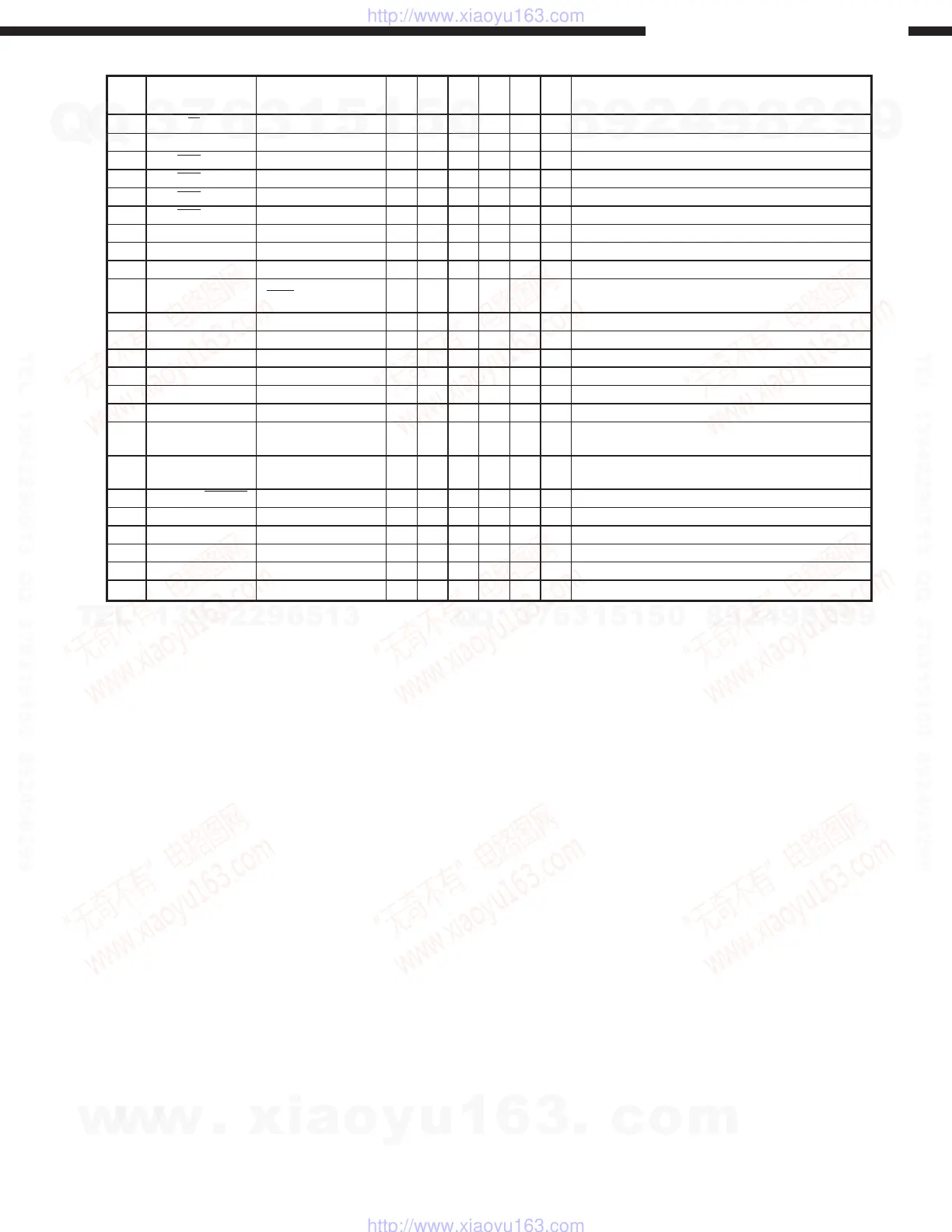

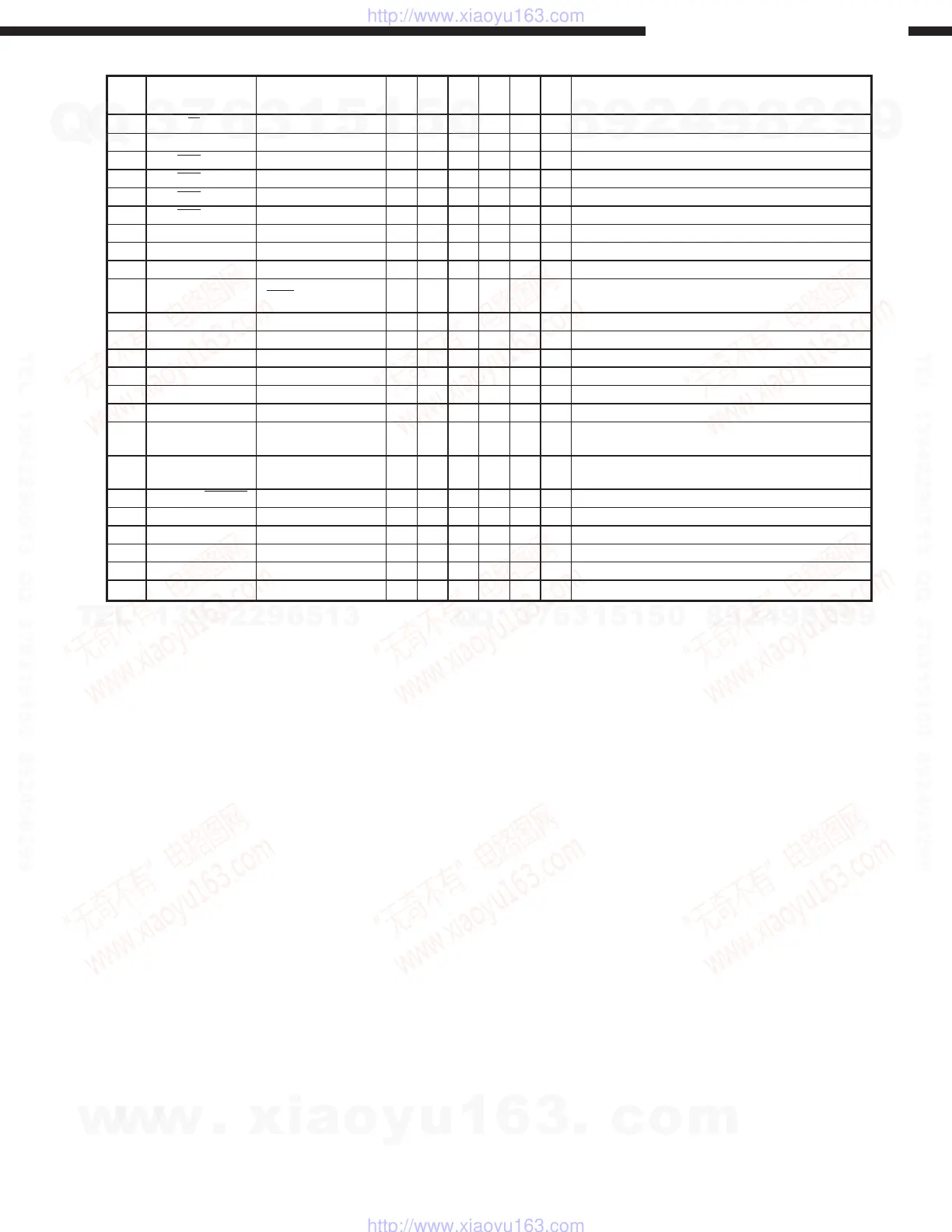

77 P36/R/W Not used I Ed H(Iu) Not used (GND)

78 P37 Not used I Ed H(Iu) Not used (GND)

79 P40/CS0 X'TALRST O C H(Iu) When clock oscillation stop for DIR: L

80 P41/CS1 DIR CE O C H(Iu) DIR control pin (LC89057W-E) chip enable output

81 P42/CS2 DIR_RST O C Ed H(Iu) DIR control pin (LC89057W-E) reset: L

82 P43/CS3 Not used I Ed H(Iu) Not used (GND)

83 P60/SCK DIR CLK O C Z DIR control pin (LC89057W-E) clock output

84 P61/SO/SDA DIR DIN O C Eu Z DIR control pin (LC89057W-E) data output

85 P62/SI/SCL DIR DOUT I Eu Z DIR control input pin (LC89057W-E) data input

86 P63/INT0 _ACK I

E↓&L

Ed Z

MAIN-SUB µcom comm. control input pin

(Ack. “L” return from MAIN µcom)

87 P64/SCOUT Not used I Z Not used (GND)

88 P65 Not used I Z Not used (GND)

89 DVCC DVCC +3V

90 P66 Not used I Z Not used (GND)

91 DVSS DVSS GND

92 P50/AN0 FLAG 1A(DSP_ACK1) I Lv Eu Z DSP host I/F comm. response input (OK: L)

93 P51/AN1 FLAG 2A(BUSY1) I Lv Eu Z

DSP operation check flag

(ADSST-MEL100:FLAG 2A) Normal: L

94 P52/AN2 FLAG 3A I Lv Eu Z

Special flag for ROM update

(ADSST-MEL100:FLAG 3A)

95 P53/AN3/ADTRG _B.DOWN I Lv Eu Z Power down detect (Power down: L)

96 P54/AN4 Not used I Lv Ed Z Not used (GND)

97 P55/AN5 Not used I Lv Ed Z Not used (GND)

98 P56/AN6 Not used I Lv Ed Z Not used (GND)

99 P57/AN7 Not used I Lv Ed Z Not used (GND)

100 VREFH VREFH I AD ref. V input pin, +3V

Pin

No.

Pin Name FunctionI/OSymbol

Type

Det

Op

(Int.)

Op

(Ext.)

Res

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...