PCM9211 (DIGITAL : IC202)

PIN Functions

PIN

DESCRIPTION

NO. NAME I/O

5-V

TOLERANT

1 ERROR/INT0 O No DIR Error detection output / Interrupt0 output

2 NPCM/INT1 O No DIR Non-PCM detection output / Interrupt1 output

3 MPIO_A0 I/O Yes Multipurpose I/O, Group A(1)

4 MPIO_A1 I/O Yes Multipurpose I/O, Group A(1)

5 MPIO_A2 I/O Yes Multipurpose I/O, Group A(1)

6 MPIO_A3 I/O Yes Multipurpose I/O, Group A(1)

7 MPIO_C0 I/O Yes Multipurpose I/O, Group C(1)

8 MPIO_C1 I/O Yes Multipurpose I/O, Group C(1)

9 MPIO_C2 I/O Yes Multipurpose I/O, Group C(1)

10 MPIO_C3 I/O Yes Multipurpose I/O, Group C(1)

11 MPIO_B0 I/O Yes Multipurpose I/O, Group B(1)

12 MPIO_B1 I/O Yes Multipurpose I/O, Group B(1)

13 MPIO_B2 I/O Yes Multipurpose I/O, Group B(1)

14 MPIO_B3 I/O Yes Multipurpose I/O, Group B(1)

15 MPO0 O No Multipurpose output 0

16 MPO1 O No Multipurpose output 1

17 DOUT O No Main output port, serial digital audio data output

18 LRCK O No Main output port, LR clock output

19 BCK O No Main output port, Bit clock output

20 SCKO O No Main output port, System clock output

21 DGND – – Ground, for digital

22 DVDD – – Power supply, 3.3 V (typ.), for digital

23 MDO/ADR0 I/O Yes Software control I/F, SPI data output / I2C slave address

setting0(2)

24 MDI/SDA I/O Yes Software control I/F, SPI data input / I2C data input/output(2)

(3)

25 MC/SCL I Yes Software control I/F, SPI clock input / I2C clock input(2)

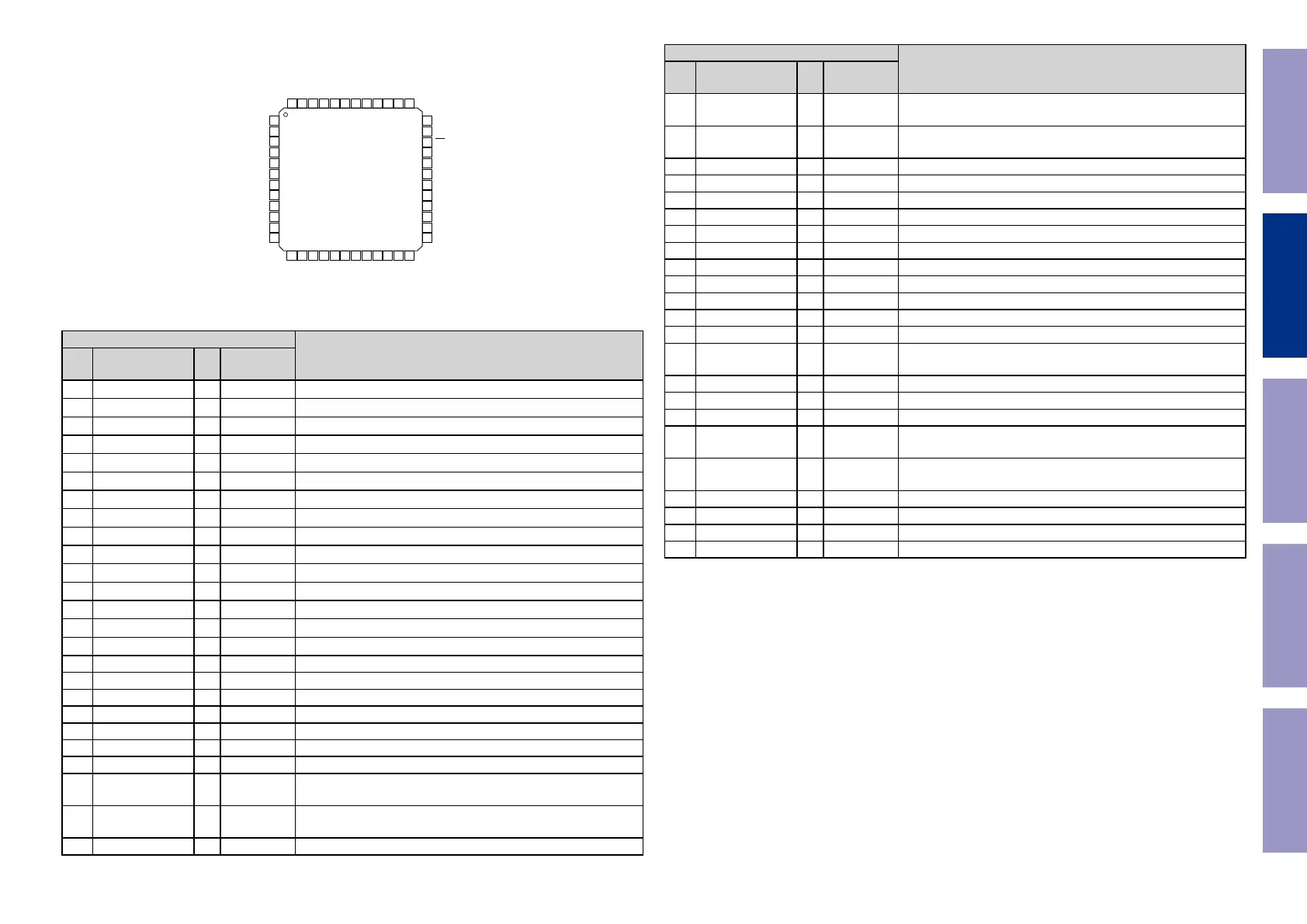

36

35

34

33

32

31

30

29

28

27

26

25

1

2

3

4

5

6

7

8

9

10

11

12

NPCM/INT1

MPIO_A0

MPIO_A1

MPIO_A2

MPIO_A3

MPIO_C0

MPIO_C1

MPIO_C2

MPIO_C3

MPIO_B0

MPIO_B1

VDDRX

RXIN1

RST

RXIN2

RXIN3

RXIN4/ASCKIO

RXIN5/ABCKIO

RXIN7/ADIN0

MODE

MS/ADR1

MC/SCL

48 47 46

45

44 43

42

41

40 39 38

13

14

15 16

17

18 19 20

21 22

23

37

24

PCM9211

VINR

VINL

VCCAD

AGNDAD

VCOM

FILT

VCC

AGND

XTO

XTI

GNDRX

RXIN0

MPIO_B2

MPIO_B3

MPO0

MPO1

DOUT

LRCK

BCK

SCKO

DGND

DVDD

MDI/SDA

PCM9211

www.ti.com

SBAS495 –JUNE 2010

PIN CONFIGURATIONS

PT PACKAGE

LQFP-48

(TOP VIEW)

PIN FUNCTIONS

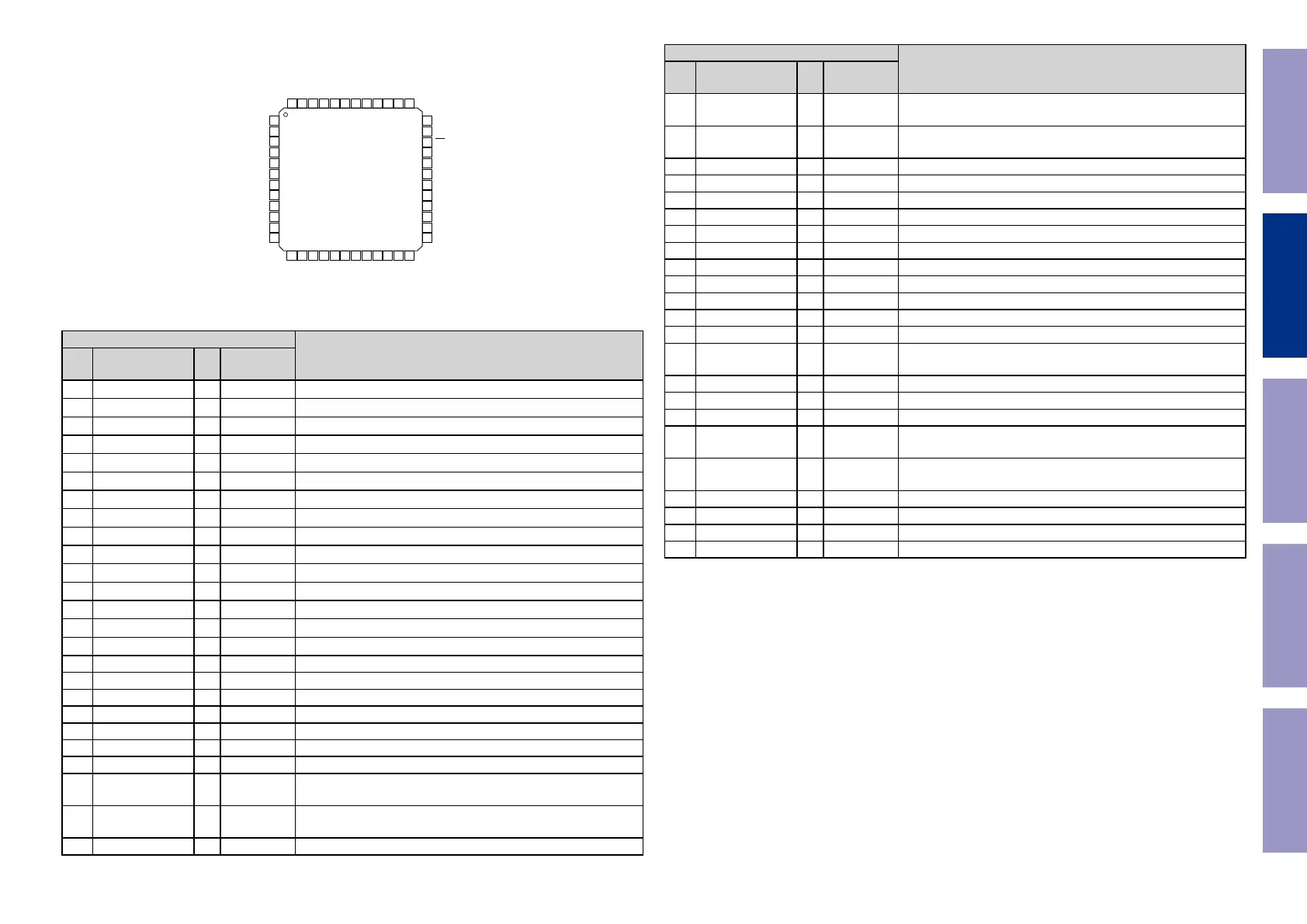

PIN

5-V

NO. NAME I/O TOLERANT DESCRIPTION

1 ERROR/INT0 O No DIR Error detection output / Interrupt0 output

2 NPCM/INT1 O No DIR Non-PCM detection output / Interrupt1 output

3 MPIO_A0 I/O Yes Multipurpose I/O, Group A

(1)

4 MPIO_A1 I/O Yes Multipurpose I/O, Group A

(1)

5 MPIO_A2 I/O Yes Multipurpose I/O, Group A

(1)

6 MPIO_A3 I/O Yes Multipurpose I/O, Group A

(1)

7 MPIO_C0 I/O Yes Multipurpose I/O, Group C

(1)

8 MPIO_C1 I/O Yes Multipurpose I/O, Group C

(1)

9 MPIO_C2 I/O Yes Multipurpose I/O, Group C

(1)

10 MPIO_C3 I/O Yes Multipurpose I/O, Group C

(1)

11 MPIO_B0 I/O Yes Multipurpose I/O, Group B

(1)

12 MPIO_B1 I/O Yes Multipurpose I/O, Group B

(1)

13 MPIO_B2 I/O Yes Multipurpose I/O, Group B

(1)

14 MPIO_B3 I/O Yes Multipurpose I/O, Group B

(1)

15 MPO0 O No Multipurpose output 0

(1) Schmitt trigger input

Copyright © 2010, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): PCM9211

PIN

DESCRIPTION

NO. NAME I/O

5-V

TOLERANT

26 MS/ADR1 I Yes Software control I/F, SPI chip select / I2C slave address

setting1(2)

27 MODE I No Control mode setting, (see the Serial Control Mode section,

Control Mode Pin Setting)

28 RXIN7/ADIN0 I Yes Biphase signal, input 7 / AUXIN0, serial audio data input(2)

29 RXIN6/ALRCKI0 I Yes Biphase signal, input 6 / AUXIN0, LR clock input(2)

30 RXIN5/ABCKI0 I Yes Biphase signal, input 5 / AUXIN0, bit clock input(2)

31 RXIN4/ASCKI0 I Yes Biphase signal, input 4 / AUXIN0, system clock input(2)

32 RXIN3 I Yes Biphase signal, input 3(2)

33 RXIN2 I Yes Biphase signal, input 2(2)

34 RST I Yes Reset Input, active low(2) (4)

35 RXIN1 I Yes Biphase signal, input 1, built-in coaxial amplier

36 VDDRX – – Power supply, 3.3 V (typ.), for RXIN0 and RXIN1.

37 RXIN0 I Yes Biphase signal, input 0, built-in coaxial amplier

38 GNDRX - - Ground, for RXIN

39 XTI I No Oscillation circuit input for crystal resonator or external XTI

clock source input(5)

40 XTO O No Oscillation circuit output for crystal resonator

41 AGND – – Ground, for PLL analog

42 VCC – – Power supply, 3.3 V (typ.), for PLL analog

43 FILT O No External PLL loop filter connection terminal; must connect

recommended lter

44 VCOM O No ADC common voltage output; must connect external

decoupling capacitor

45 AGNDAD – – Ground, for ADC analog

46 VCCAD – – Power supply, 5.0 V (typ.), for ADC analog

47 VINL I No ADC analog voltage input, left channel

48 VINR I No ADC analog voltage input, right channel

(1) Schmitt trigger input

(2) Schmitt trigger input

(3) Open-drain conguration in I2C mode

(4) Onboard pull-down resistor (50 k Ω , typical)

(5) CMOS Schmitt trigger input

Before Servicing

This Unit

Electrical Mechanical Repair Information Updating

66

Loading...

Loading...