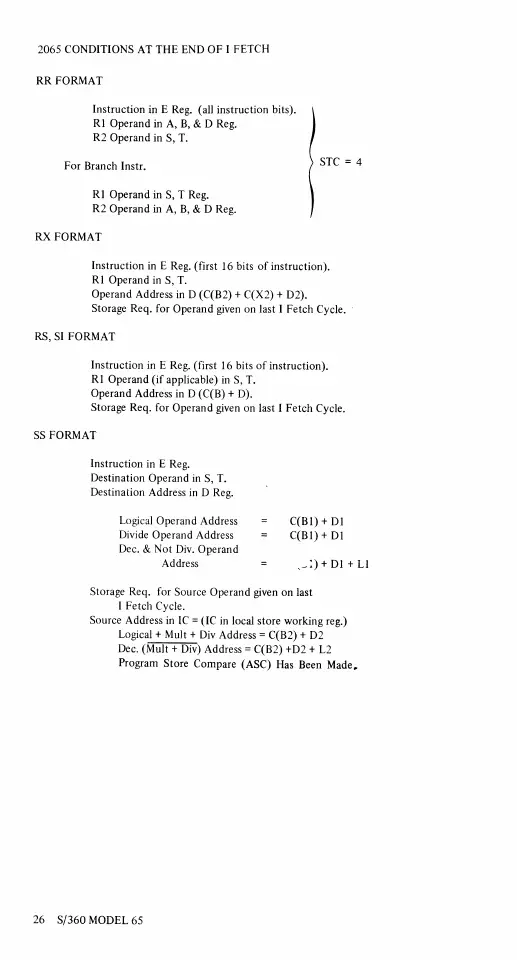

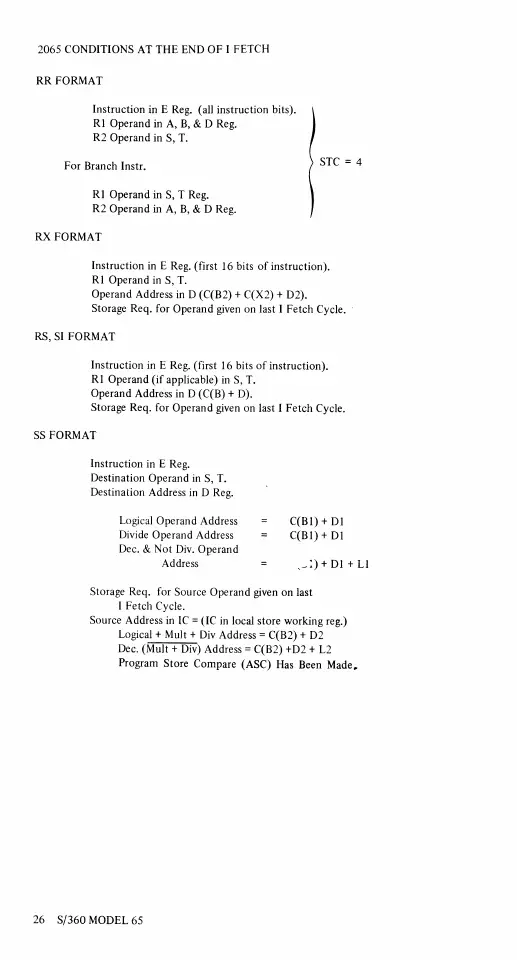

2065

CONDITIONS AT

THE

END

OF

I FETCH

RR

FORMAT

Instruction in E Reg. (all instruction bits).

R 1

Operand

in A,

B,

&

DReg.

R2

Operand

in

S, T.

For Branch Instr.

Rl Operand in S, T Reg.

R2

Operand

in A,

B,

&

DReg.

RXFORMAT

STC = 4

Instruction

in

E Reg. (first 16 bits

of

instruction).

Rl

Operand in

S,

T.

Operand

Address

in

D (C(B2) +

C(Xl)

+ 02).

Storage Req. for Operand given on last I Fetch Cycle.

RS.

SI

FORMAT

Instruction

in

E Reg. (first 16 bits

of

instruction).

Rl

Operand

(if

applicable)

in

S, T.

Operand Address in 0 «('(8)

+ D).

Storage Req. for Operand

given

on last 1 Fetch Cycle.

SS

FORMAT

Instruction

III

E Reg.

Destmation Operand

1Il

S,

T.

Destination Address in

DReg.

Logical

Operand

Address

DIvide

Operand

Address

Dec.

& Not Div. Operalld

Address

e(BI)

+ DI

C(81) + DI

Storage Rcq. for Source Operand given

on last

I Fetch Cycle.

Source Address

in

Ie

==

(Ie

in

local

store

working reg.)

Logical

+ Mult + Div Address:::

C(82)

+ D2

Dec.

(Mult

+ Div) Address = C(B2) +D2 + L2

Program

Store

Compare (ASC) Has Been Made

..

26

S/360

MODEL

65

Loading...

Loading...