DTR-5.9

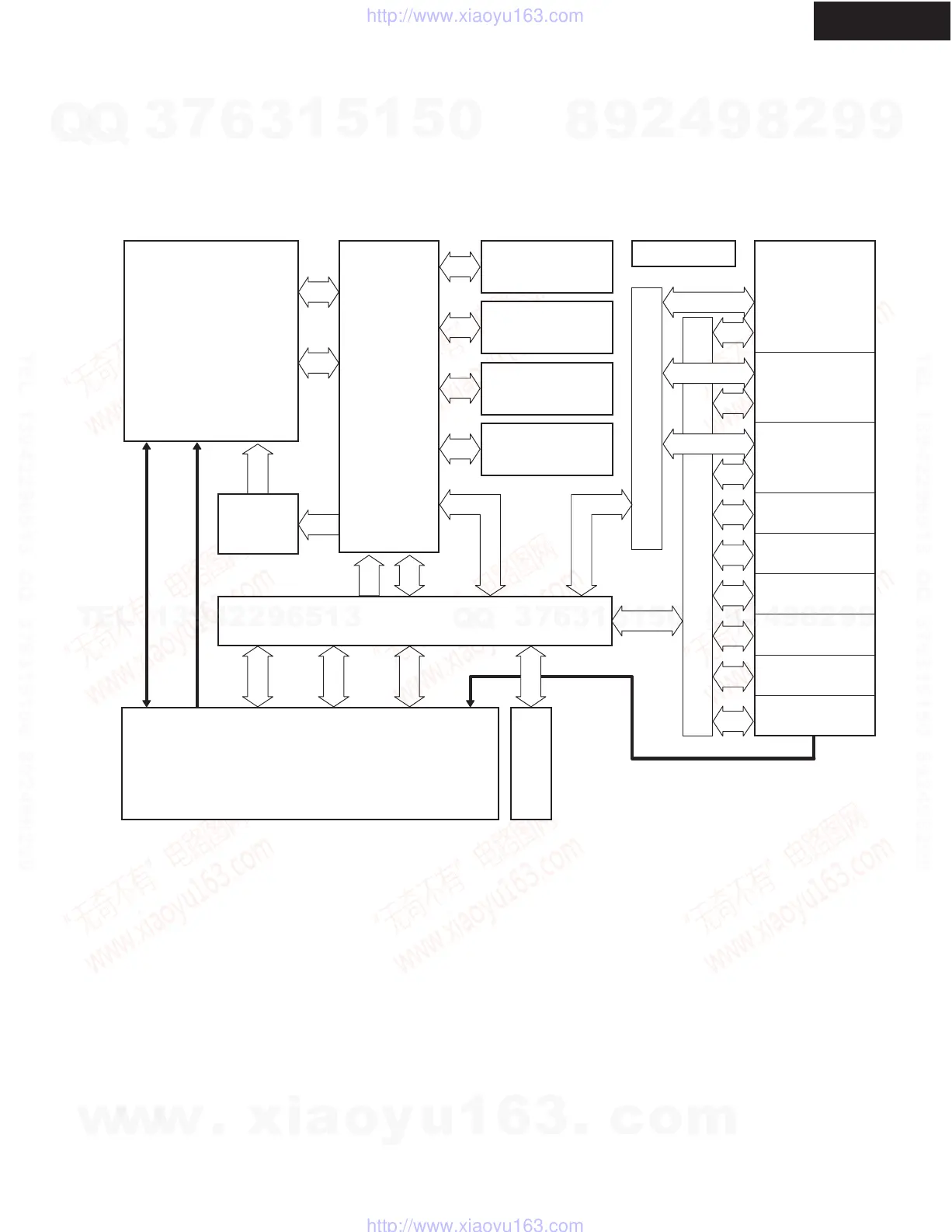

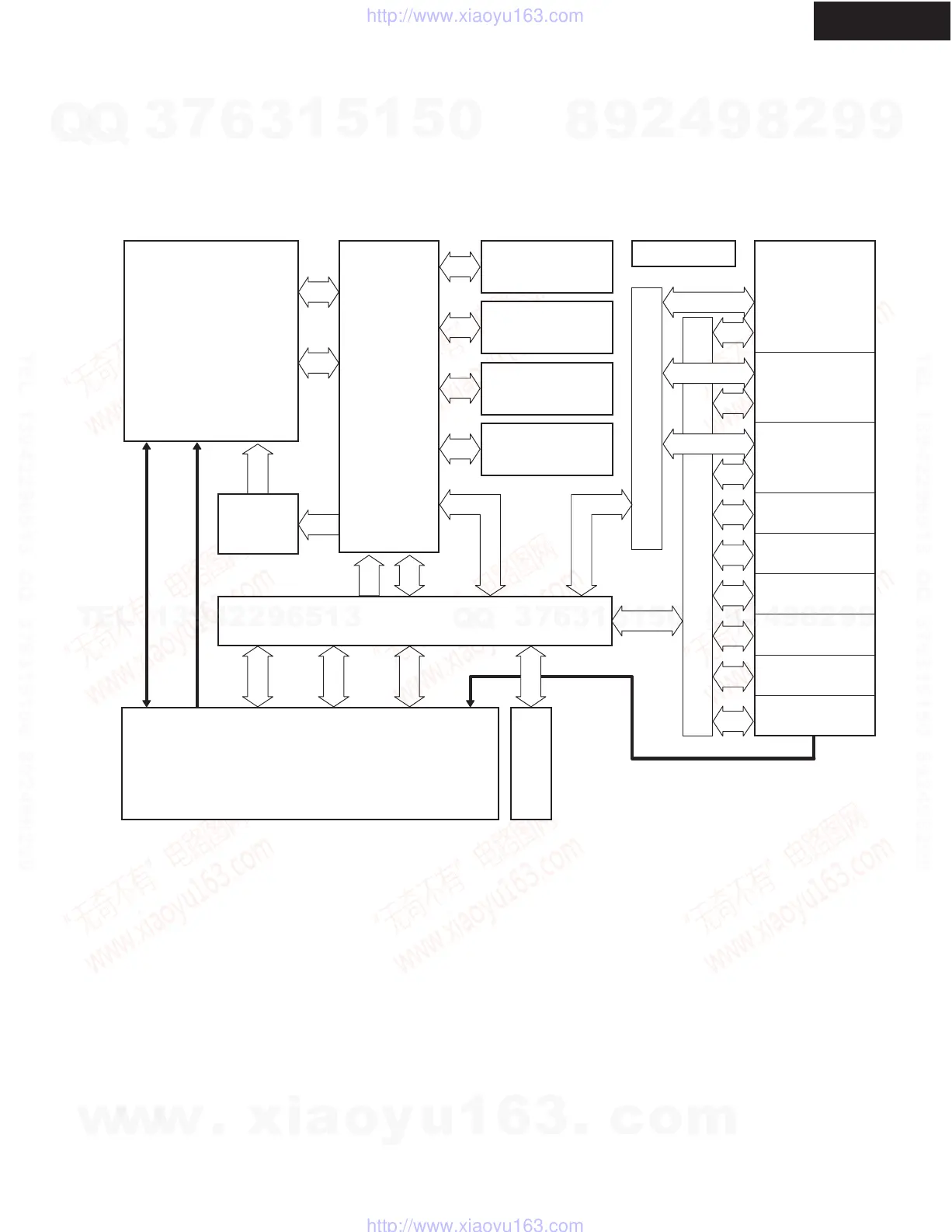

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS-1

Q201 : D788E001BRFP266 (Floating-Point Digital Signal Processor)-1/5

BLOCK DIAGRAM

256

256

256

256

3232

DMPPMP

CSP

32

256

64

D1

Data

R/W

R/W

Data

D2

64

256

Program

Fetch

INTI/O

C67x + CPU

Memory

Controller

32

High-Performance

Crossbar Switch

32

McASP DMA Bus

32

32

32

32

32

32

32

Peripheral Configuration Bus

EMIF

32

Events

In

32

MAX1MAX0

32

CONTROL

32

Interrupts

Out

I/O

dMAX

32

32

32

32

32

McASP0

16 Serializers

McASP1

6 Serializers

McASP2

2 Serializers

DIT Only

SPI1

SPI0

I2C1

I2C0

RTI

PLL

JTAG EMU

Program/Data

RAM

256K Bytes

Program/Data

ROM Page1

256K Bytes

Program/Data

ROM Page3

256K Bytes

Program/Data

ROM Page2

256K Bytes

Program

Cache

32K Bytes

Peripheral Interrupt and DMA Events

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...