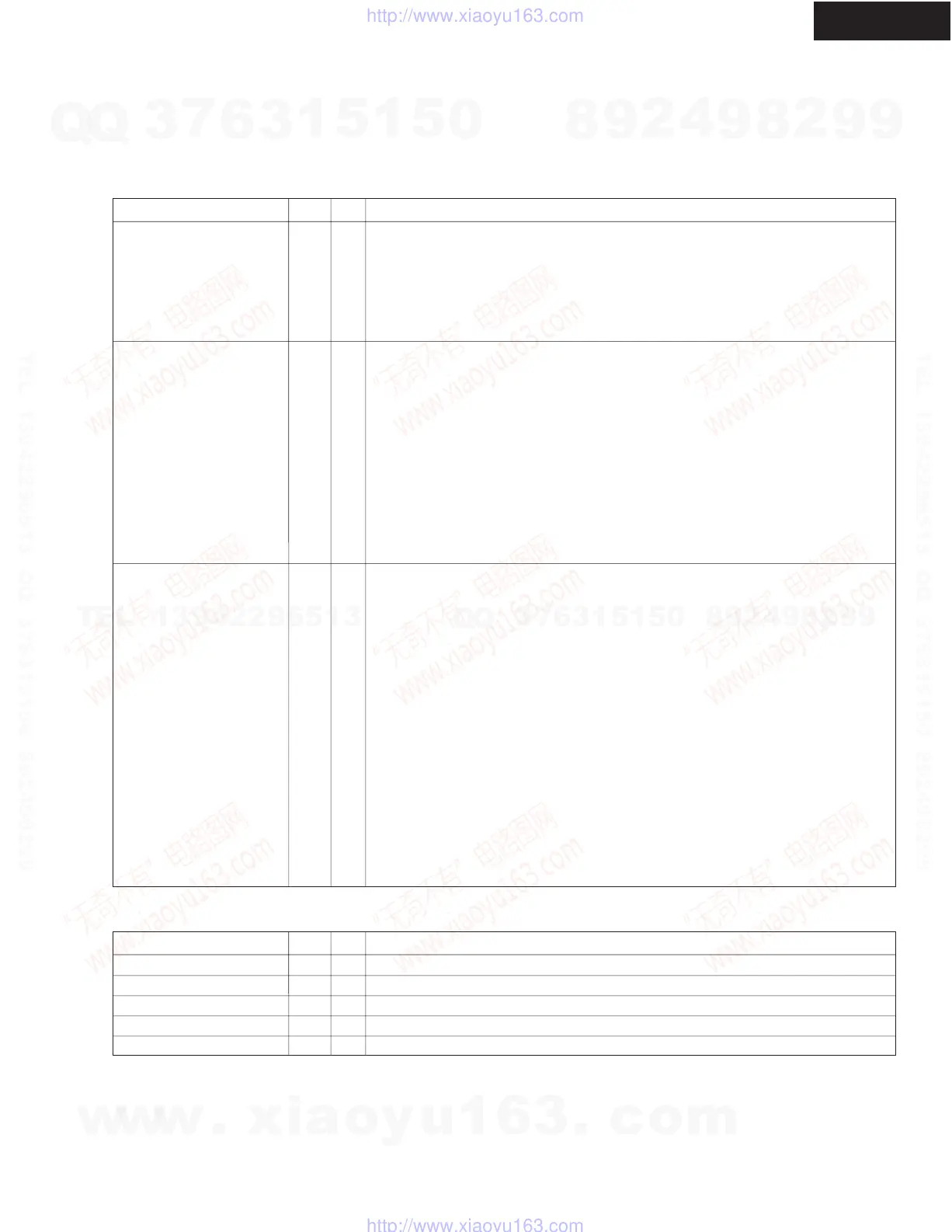

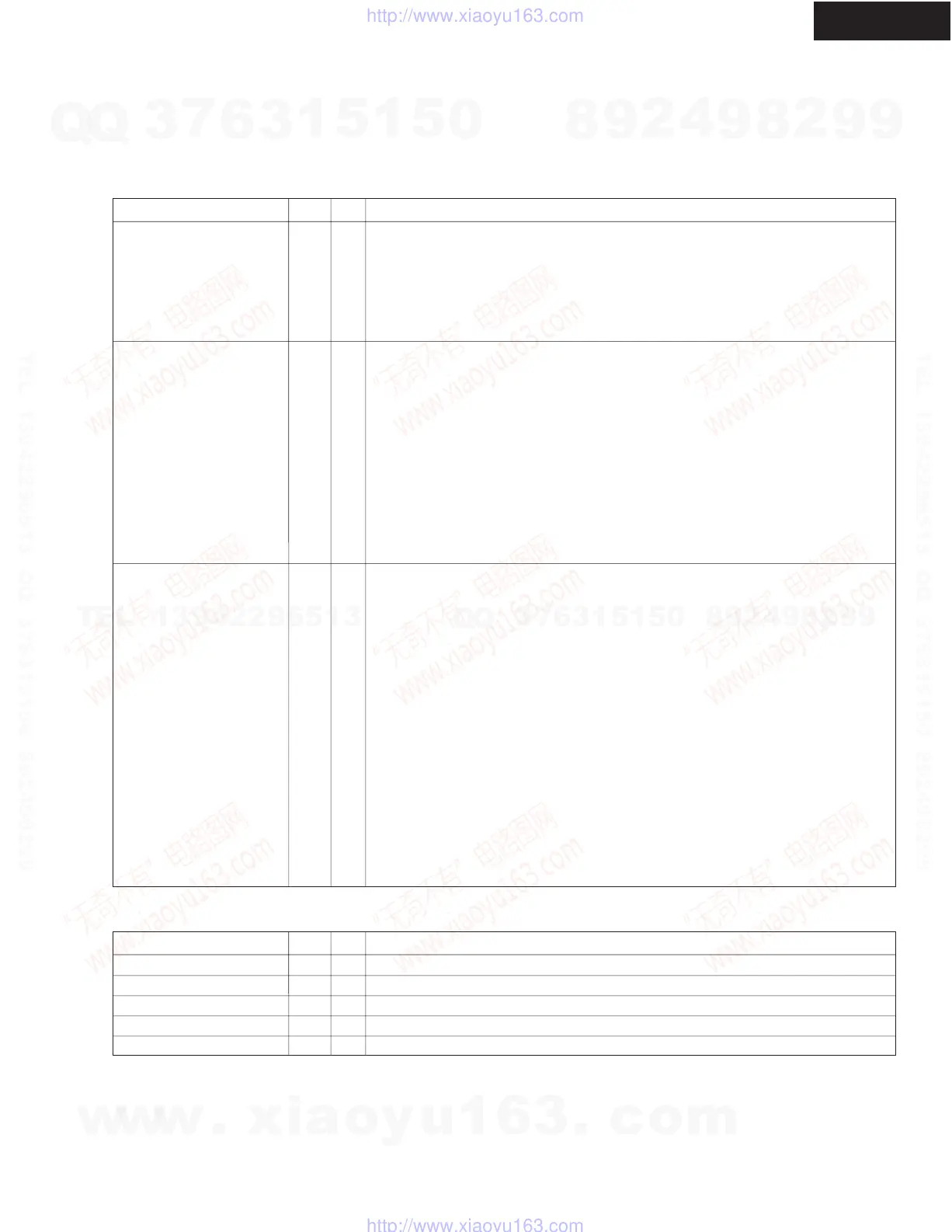

DTR-5.9

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS-29

Q8001 : FLI30502 (LCD TV Controller with Worldwide Standard Sound Processor

and HDMI Receiver)-11/12

TERMINAL DESCRIPTION

Digital Power and Ground

I/O

P

P

G

Description

Ring VDD. Connect to digital 3.3 V.

Core VDD. Connect to digital 3.3V.

Chip ground for core and ring.

Pin Name

RVDD_3.3

CVDD_1.8

CRVSS

Pin #

30

47

110

128

152

172

20

26

37

43

51

65

103

131

134

143

158

21

27

31

38

44

48

52

66

104

111

129

132

135

144

153

159

I/O

I

O

I

I

I

Description

JTAG CLOCK signal

JTAG Mode signal

JTAG RESET aignal

JTAG DATA OUT signal

JTAG DATA IN signal

Pin Name

JTAG_CLK

JTAG_MODE

JTAG_RESET

JTAG_TDO

JTAG_TDI

Pin #

22

23

49

154

155

OCM JTAG

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...