24 Intel

®

440Bx Scalable Performance Board Development Kit Manual

Theory of Operation

3.2.14 USB

USB support is provided through the 82371EB PCI-to-ISA/IDE Xcelerator (PIIX4E) and can be

used through connector J2.

3.2.15 RS232 Ports

Two serial I/O ports provided by the SMC FDC37B787 SuperI/O device. Two 9-pin RS232

connectors are provided on a single stacked connector (J4).

3.2.16 IEEE 1284 Parallel Port

One 25-pin IEEE 1284 parallel port connector controlled by the SMC FDC37B787 SuperI/O

device is provided (J3).

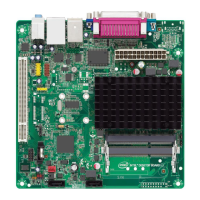

3.2.17 PCI Connectors

Three industry standard 32-bit, 5-V PCI connectors are provided on the evaluation board. The

connectors are designed to handle either a 5-V only card or a universal card. 3.3-V cards are not

supported.

3.2.18 ISA Connectors

Two 16-bit ISA connectors are provided on the evaluation board.

3.2.19 AGP Connector

AGP support is provided through the 82443BX Host Bridge/Controller. One industry standard

AGP connector (J13) is provided on the evaluation board.

3.2.20 Post Code Debugger

The evaluation board has an on-board Post Code Debugger. Data from any program that does an I/

O write to 0080H is latched and displayed on the two LEDs (U12 and U13). During BIOS startup,

codes are posted to these LEDs to indicate what the BIOS is doing. Application programs can post

their own data to these LEDs by writing to I/O address 0080H.

3.2.21 Clock Generation

There are two devices on the baseboard which generate and distribute the clocks used by the entire

system. These are the CY2280 clock synthesizer and the CY2318NZ clock buffer.

The CY2280 generates the clocks for the PGA370 processor, Host Bridge/Controller, cache, PCI,

USB and ISA bus. The processor side bus clock runs at 66 or 100 MHz. The PCI clocks run at

33 MHz. This device is capable of spread spectrum clocking. If spread spectrum clocking is

enabled, a 0.5% down spread will be introduced in the processor and PCI clocks.