GD82559ER — Networkin

Silicon

8

Datasheet

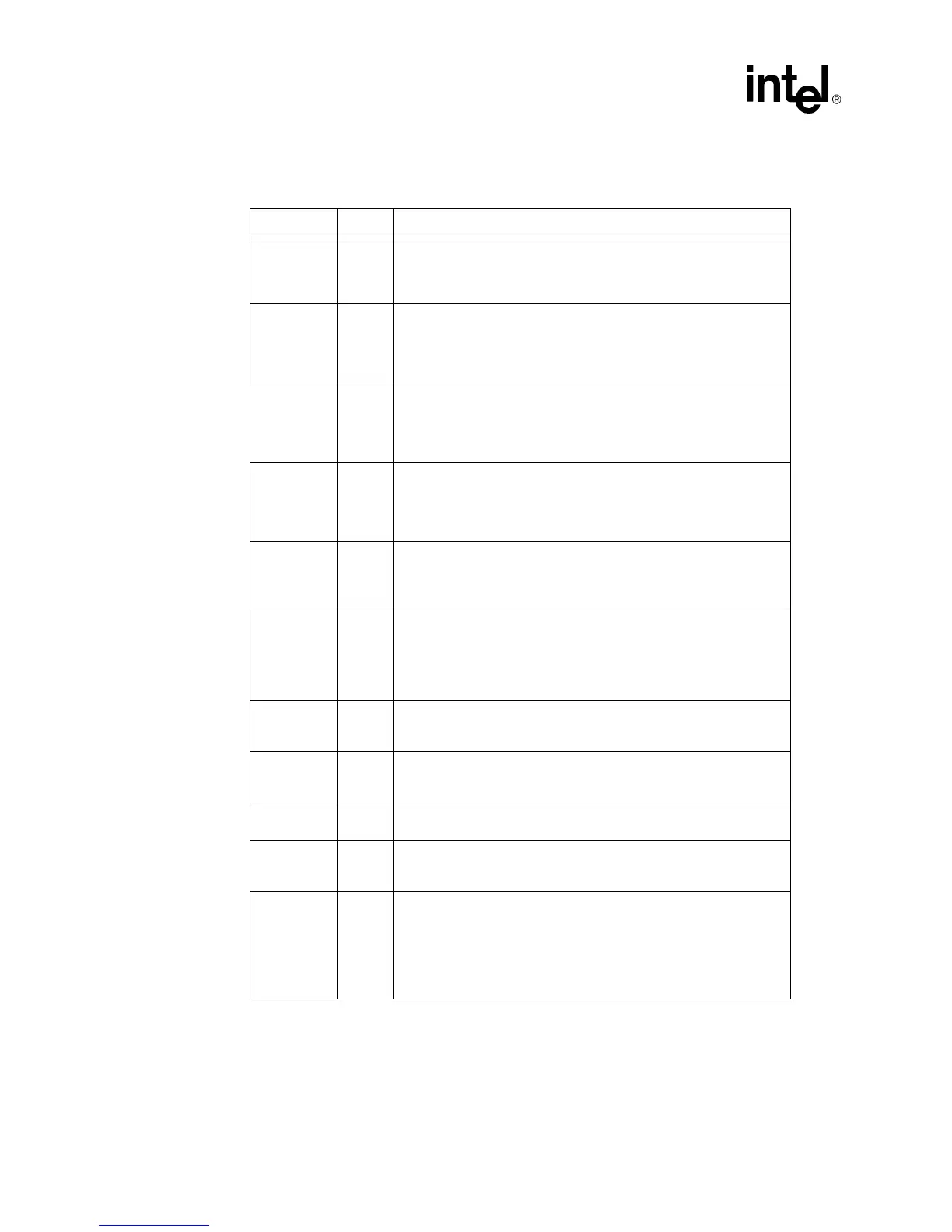

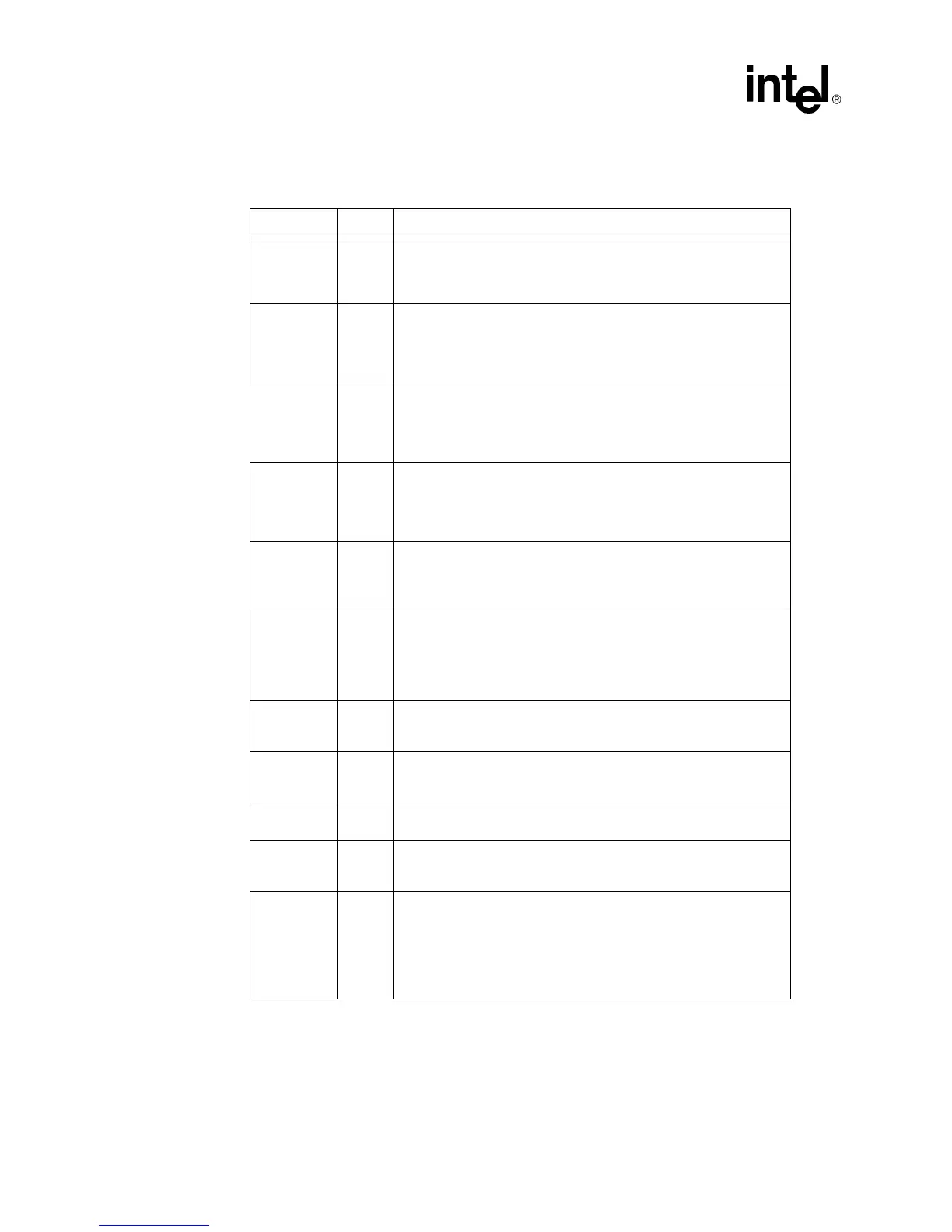

3.2.2 Interface Control Si

nals

Symbol Type Name and Function

FRAME# S/T/S

Cycle Frame.

The c

cle frame si

nal is driven b

the current master

to indicate the be

innin

and duration of a transaction. FRAME# is

asserted to indicate the start of a transaction and de-asserted durin

the final data phase.

IRDY# S/T/S

Initiator Ready.

The initiator read

si

nal indicates the bus master’s

abilit

to complete the current data phase and is used in con

unction

with the tar

et read

TRDY#

si

nal. A data phase is completed on

an

clock c

cle where both IRDY# and TRDY# are sampled asserted

low

simultaneousl

.

TRDY# S/T/S

Target Ready.

The tar

et read

si

nal indicates the selected device’s

abilit

to complete the current data phase and is used in con

unction

with the initiator read

IRDY#

si

nal. A data phase is completed on

an

clock c

cle where both IRDY# and TRDY# are sampled asserted

low

simultaneousl

.

STOP# S/T/S

Stop.

The stop si

nal is driven b

the tar

et to indicate to the initiator

that it wishes to stop the current transaction. As a bus slave, STOP# is

driven b

the 82559ER to inform the bus master to stop the current

transaction. As a bus master, STOP# is received b

the 82559ER to

stop the current transaction.

IDSEL IN

Initialization Device Select.

The initialization device select si

nal is

used b

the 82559ER as a chip select durin

PCI confi

uration read

and write transactions. This si

nal is provided b

the host in PCI

s

stems.

DEVSEL# S/T/S

Device Select.

The device select si

nal is asserted b

the tar

et once

it has detected its address. As a bus master, the DEVSEL# is an input

si

nal to the 82559ER indicatin

whether an

device on the bus has

been selected. As a bus slave, the 82559ER asserts DEVSEL# to

indicate that it has decoded its address as the tar

et of the current

transaction.

REQ# T/S

Request.

The re

uest si

nal indicates to the bus arbiter that the

82559ER desires use of the bus. This is a point-to-point si

nal and

ever

bus master has its own REQ#.

GNT# IN

Grant.

The

rant si

nal is asserted b

the bus arbiter and indicates to

the 82559ER that access to the bus has been

ranted. This is a point-

to-point si

nal and ever

master has its own GNT#.

INTA# O/D

Interrupt A.

The interrupt A si

nal is used to re

uest an interrupt b

the 82559ER. This is an active low, level tri

ered interrupt si

nal.

SERR# O/D

System Error.

The s

stem error si

nal is used to report address

parit

errors. When an error is detected, SERR# is driven low for a

sin

le PCI clock.

PERR# S/T/S

Parity Error.

The parit

error si

nal is used to report data parit

errors

durin

all PCI transactions except a Special C

cle. The parit

error pin

is asserted two clock c

cles after the error was detected b

the device

receivin

data. The minimum duration of PERR# is one clock for each

data phase where an error is detected. A device cannot report a parit

error until it has claimed the access b

assertin

DEVSEL# and

completed a data phase.

Loading...

Loading...