Datasheet

55

Networkin

Silicon — GD82559ER

7.1.19 Power Mana

ement Control/Status Re

ister

PMCSR

The Power Management Control/Status is a word register. It is used to determine and change the

current power state of the 82559ER and control the power management interrupts in a standard

manner.

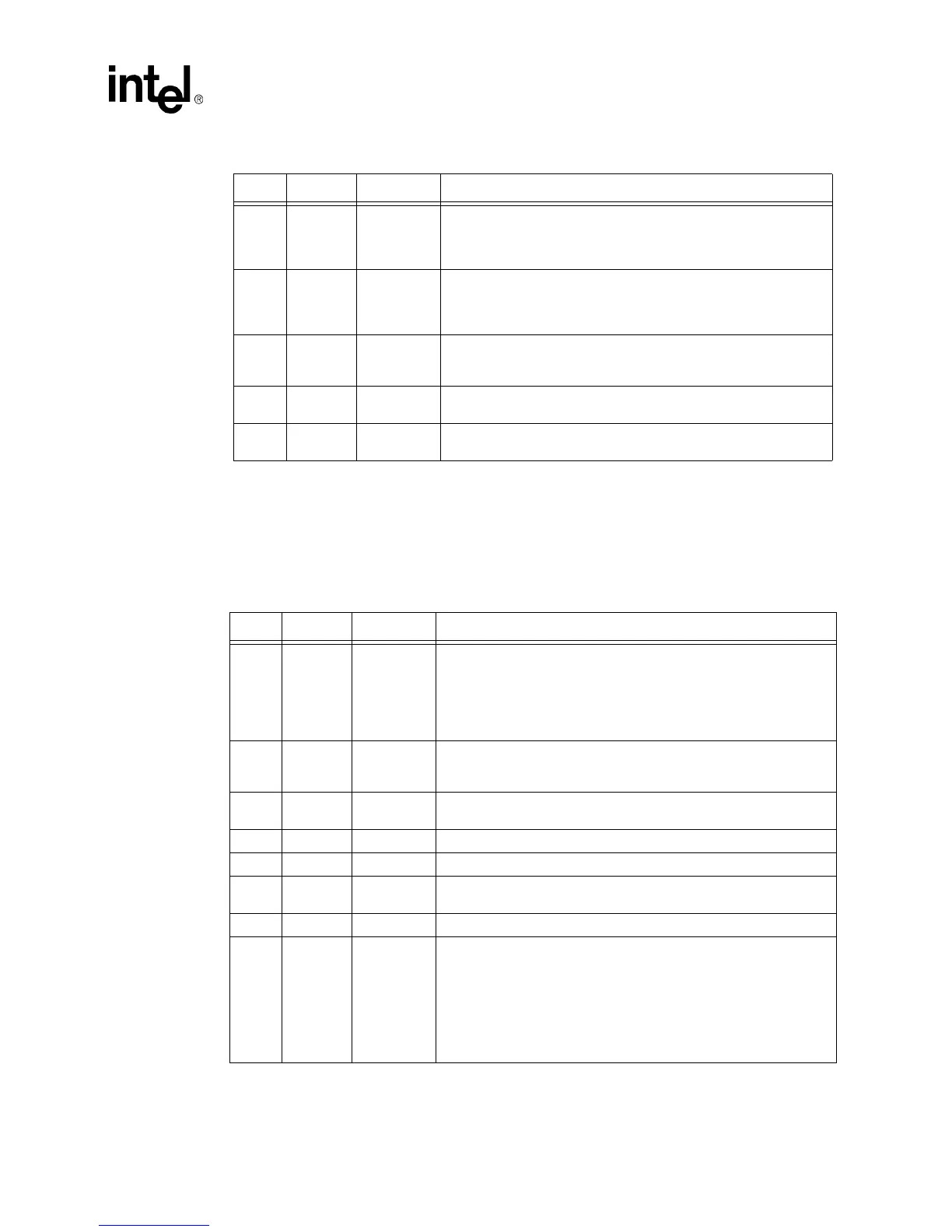

24:22 000b Read Onl

Auxiliary Current.

This field reports whether the 82559ER

implements the Data re

isters. The auxiliar

power consumption is

the same as the current consumption reported in the D3 state in the

Data re

ister.

21 1b Read Onl

Device Specific Initialization (DSI).

The DSI bit indicates whether

special initialization of this function is re

uired

be

ond the standard

PCI confi

uration header

before the

eneric class device driver is

able to use it. DSI is re

uired for the 82559ER after D3-to-D0 reset.

20 0b

PCI

Read Onl

Reserved (PCI).

When this bit is set to ‘1’, it indicates that the

82559ER re

uires auxiliar

power supplied b

the s

stem for wake-

up from the D3

cold

state.

19 0b Read Onl

PME Clock.

The 82559ER does not re

uire a clock to

enerate a

power mana

ement event.

18:16 010b Read Onl

Version.

A value of indicates that the 82559ER complies with the PCI

Power Mana

ement Specification, Revision 2.2.

Table 8. Power Mana

ement Ca

abilit

Re

ister

Bits Default Read/Write Description

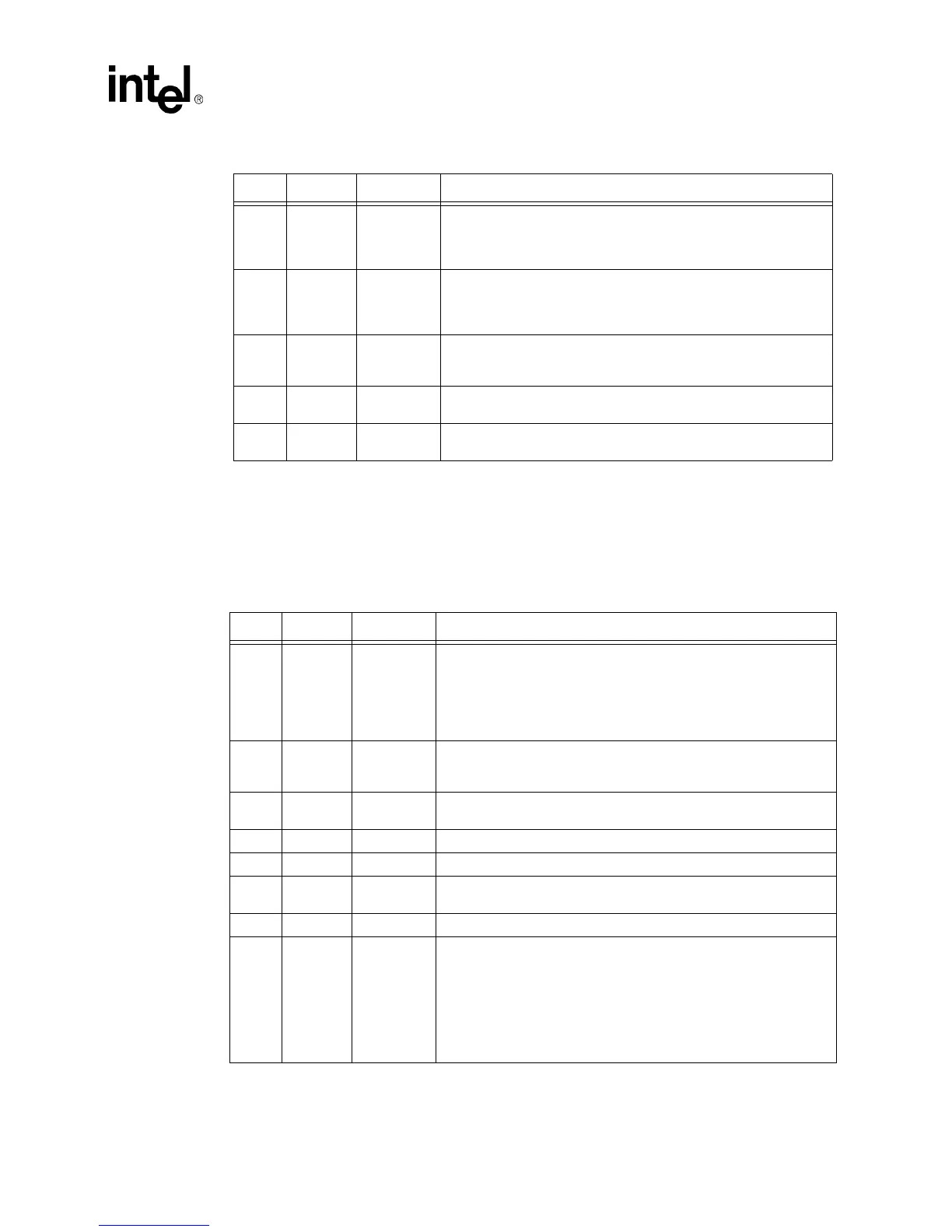

Table 9. Power Mana

ement Control and Status Re

ister

Bits Default Read/Write Description

15 0b Read/Clear

PME Status.

This bit is set upon a wake-up event. It is independent of

the state of the PME Enable bit. If 1b is written to this bit, the bit will be

cleared. It also de-asserts the PME# si

nal and clears the PME status

bit in the Power Mana

ement Driver Re

ister. When the PME# si

nal

is enabled, the PME# si

nal reflects the state of the PME status bit.

14:13 00b Read Onl

Data Scale.

This field indicates the data re

ister scalin

factor. It

e

uals 10b for re

isters zero throu

h ei

ht and 00b for re

isters nine

throu

h fifteen.

12:9 0000b Read Onl

Data Select.

This field is used to select which data is reported throu

h

the Data re

ister and Data Scale field.

8 0b Read Clear

PME Enable.

This bit enables the 82559ER to assert PME#.

7:5 000b Read Onl

Reserved

. These bits are reserved and should be set to 000b.

4 0b Read Onl

Dynamic Data.

The 82559ER does not support the abilit

to monitor

the power consumption d

namicall

.

3:2 00b Read Onl

Reserved.

These bits are reserved and should be set to 00b.

1:0 00b Read/Write

Power State.

This 2-bit field is used to determine the current power

state of the 82559ER and to set the 82559ER into a new power state.

The definition of the field values is as follows.

00 - D0

01 - D1

10 - D2

11 - D3

Loading...

Loading...