Do you have a question about the Intel CELERON 1.10 GHZ and is the answer not in the manual?

Defines terms used in the document, including signal naming conventions.

Explains terminology related to processor packages like S.E.P., PPGA, FC-PGA, and FC-PGA2.

Details the naming conventions for Intel Celeron processors and their identification.

Explains the GTL signaling technology and VREF usage for system bus signals.

Describes processor power states and clock control mechanisms for power saving.

Describes the standard operating state of the processor.

Details the AutoHALT power-down state entered via the HALT instruction.

Explains the Stop-Grant state entered when STPCLK# is asserted.

Describes the state entered during snoop transactions while in Stop-Grant or AutoHALT.

Details the very low power Sleep state that maintains context.

Describes the lowest power Deep Sleep state entered by stopping BCLK input.

Explains the role of BCLK and PICCLK in processor operation and power states.

Details the power and ground pins used for voltage identification and power distribution.

Highlights the critical requirement for PLL power delivery with a low pass filter.

Explains the need for decoupling capacitance to manage current swings.

Discusses high-frequency decoupling requirements for AGTL+ bus operation.

Describes the VID pins used for automatic VCCCORE voltage selection.

Advises on handling and connecting unused processor pins to avoid malfunctions.

Groups Celeron processor system bus signals by buffer type for discussion.

Differentiates synchronous and asynchronous signal behavior on the system bus.

Explains the function of BSEL pins for selecting system bus frequency.

Provides recommendations for connecting to the Test Access Port logic.

Lists the absolute maximum and minimum ratings for the Celeron processor.

Details the DC specifications for the Celeron processor, including AGTL+ and CMOS signals.

Specifies AGTL+ bus routing and termination requirements.

Defines system bus timings at processor edge fingers and core pins.

Provides BCLK signal quality specifications and measurement guidelines.

Lists BCLK signal quality specifications for simulation at the processor core.

Provides AGTL+ signal quality specifications and measurement guidelines.

Lists AGTL+ signal ringback tolerance specs at the processor core for S.E.P. and PPGA.

Lists AGTL+ signal ringback tolerance specs at processor pins for FC-PGA/FC-PGA2.

Details non-AGTL+ signal quality parameters: overshoot, ringback, and settling limit.

Explains overshoot/undershoot guidelines and potential damage from violations.

Defines ringback as a reflection seen after signal switching and its impact.

Defines settling limit as maximum ringing before next transition.

Provides AGTL+ signal quality specs and measurement guidelines for FC-PGA/FC-PGA2.

Explains overshoot/undershoot guidelines for FC-PGA/FC-PGA2 packages.

Describes overshoot/undershoot magnitude measurement for FC-PGA/FC-PGA2 packages.

Defines pulse duration for overshoot/undershoot events for FC-PGA/FC-PGA2 packages.

Explains Activity Factor and its relevance to signal quality for FC-PGA/FC-PGA2.

Guides on how to read overshoot/undershoot specification tables for FC-PGA/FC-PGA2.

Provides guidelines to determine if a system meets overshoot/undershoot specifications.

Details non-AGTL+ signal quality parameters: overshoot, ringback, and settling limit.

Details processor power and heatsink design targets and case temperatures.

Explains the on-die thermal diode used for monitoring die temperature.

Defines mechanical specifications and signal definitions for the S.E.P. Package.

Describes retention mechanism requirements and substrate dimensions for S.E.P. package.

Provides signal definitions and locations for the S.E.P. package edge connector.

Defines mechanical specifications and signal definitions for the PPGA package.

Provides information for designing a heatsink and clip for the PPGA package.

Provides a pin-side view and listing of signals for the PPGA package.

Defines mechanical specifications and signal definitions for FC-PGA and FC-PGA2 packages.

Provides package dimensions and pin-side capacitor locations for the FC-PGA package.

Provides package dimensions and pin-side capacitor locations for the FC-PGA2 package.

Illustrates volumetric and component keep-out zones for the FC-PGA2 package.

Provides pin definitions and a pin-side view for FC-PGA/FC-PGA2 packages.

Shows processor top-side markings for identification purposes.

Provides guidelines for ensuring sufficient space for heatsink installation without interference.

Details mechanical specifications for boxed Intel Celeron processors and their heatsinks.

Documents mechanical specs for the boxed processor fan heatsink in S.E.P. package.

Documents mechanical specs for the boxed processor fan heatsink in PPGA package.

Documents mechanical specs for the boxed processor fan heatsink in FC-PGA/FC-PGA2 packages.

Describes cooling requirements for fan heatsink solutions used with boxed processors.

Details boxed processor cooling requirements, focusing on airflow and airspace.

Details boxed processor cooling requirements, focusing on airflow and airspace.

Addresses installation of the thermal cooling solution clip and potential PCB interference.

Details electrical requirements for the boxed Intel Celeron Processor.

Covers fan heatsink power supply and signal specifications.

Lists Celeron processor output, input, and I/O signals by category.

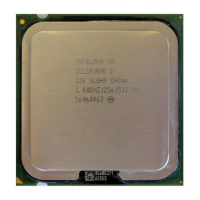

| Model | Intel Celeron 1.10 GHz |

|---|---|

| Base Clock Speed | 1.10 GHz |

| Cores | 1 |

| Threads | 1 |

| Socket Type | Socket 370 |

| Lithography | 180 nm |

| Manufacturing Process | 180 nm |