Datasheet 127

Intel

®

Celeron

®

Processor up to 1.10 GHz

NOTE:

1. Synchronous assertion with active TRDY# ensures synchronization.

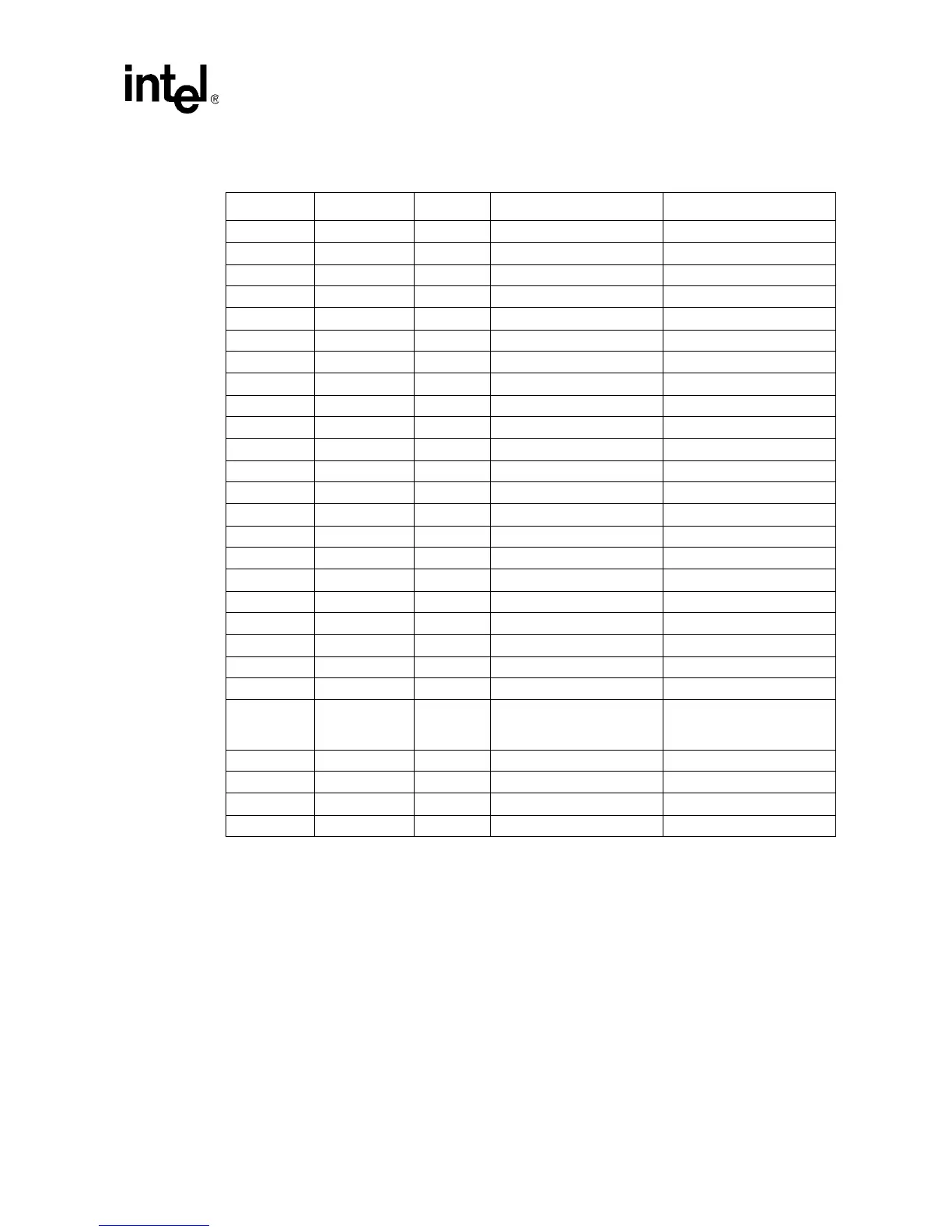

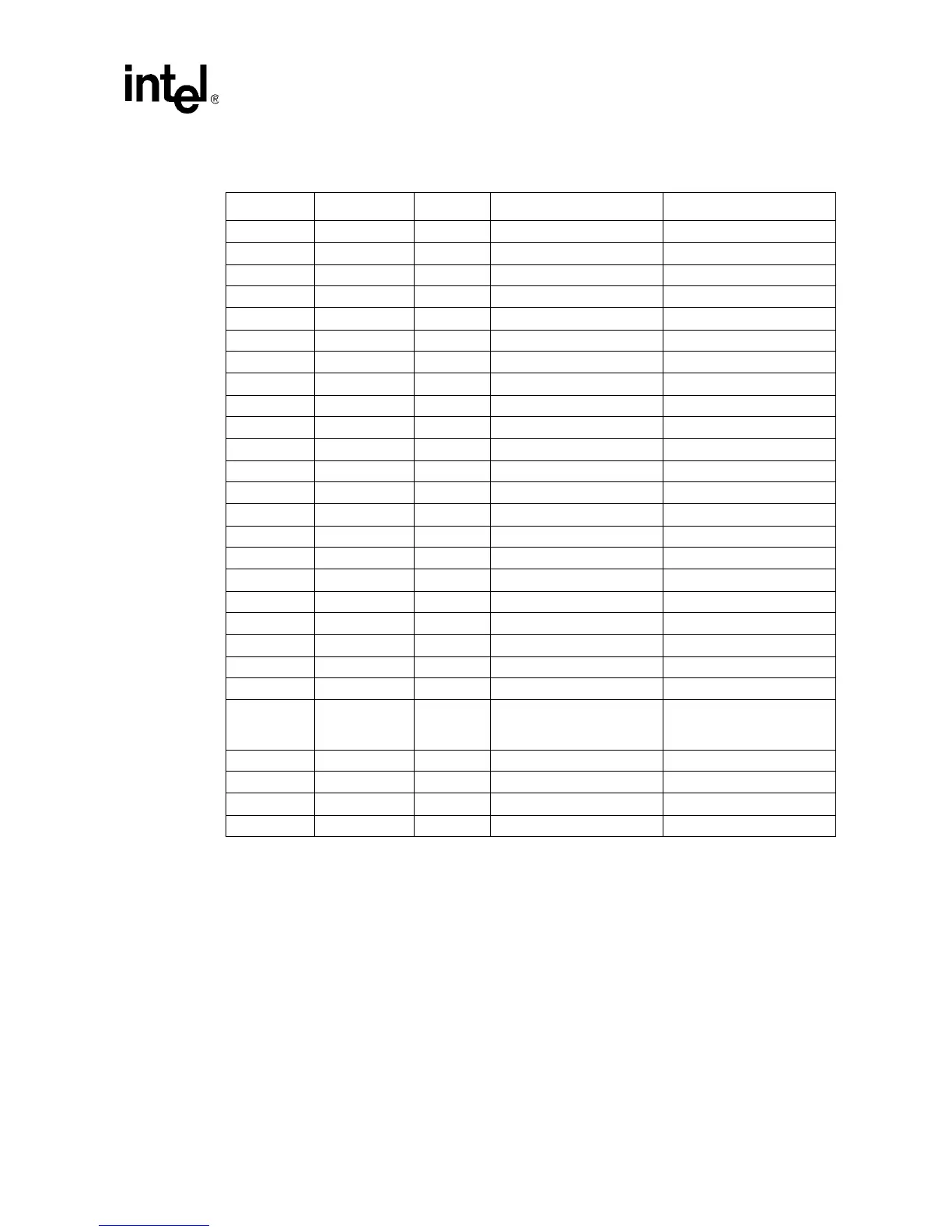

Table 61. Input Signals

Name Active Level Clock Signal Group Qualified

A20M# Low Asynch CMOS Input Always

1

BPRI# Low BCLK AGTL+ Input Always

BCLK High — System Bus Clock Always

DEFER# Low BCLK AGTL+ Input Always

FLUSH# Low Asynch CMOS Input Always

1

IGNNE# Low Asynch CMOS Input Always

1

INIT# Low Asynch CMOS Input Always

1

INTR High Asynch CMOS Input APIC disabled mode

LINT[1:0] High Asynch CMOS Input APIC enabled mode

NMI High Asynch CMOS Input APIC disabled mode

PICCLK High — APIC Clock Always

PREQ# Low Asynch CMOS Input Always

PWRGOOD High Asynch CMOS Input Always

RESET# Low BCLK AGTL+ Input Always

RS[2:0]# Low BCLK AGTL+ Input Always

RTTCTRL N/A Asynch Power/Other

SLEWCTRL N/A Asynch Power/Other

SLP# Low Asynch CMOS Input During Stop-Grant state

SMI# Low Asynch CMOS Input

STPCLK# Low Asynch CMOS Input

TCK High — TAP Input

TDI High TCK TAP Input

TESTHI

(S.E.P.P.

only)

High Asynch Power/Other Always

THERMDP N/A Asynch Power/Other

TMS High TCK TAP Input

TRST# Low Asynch TAP Input

TRDY# Low BCLK AGTL+ Input

Loading...

Loading...