Datasheet

15

Networkin

Silicon — GD82559ER

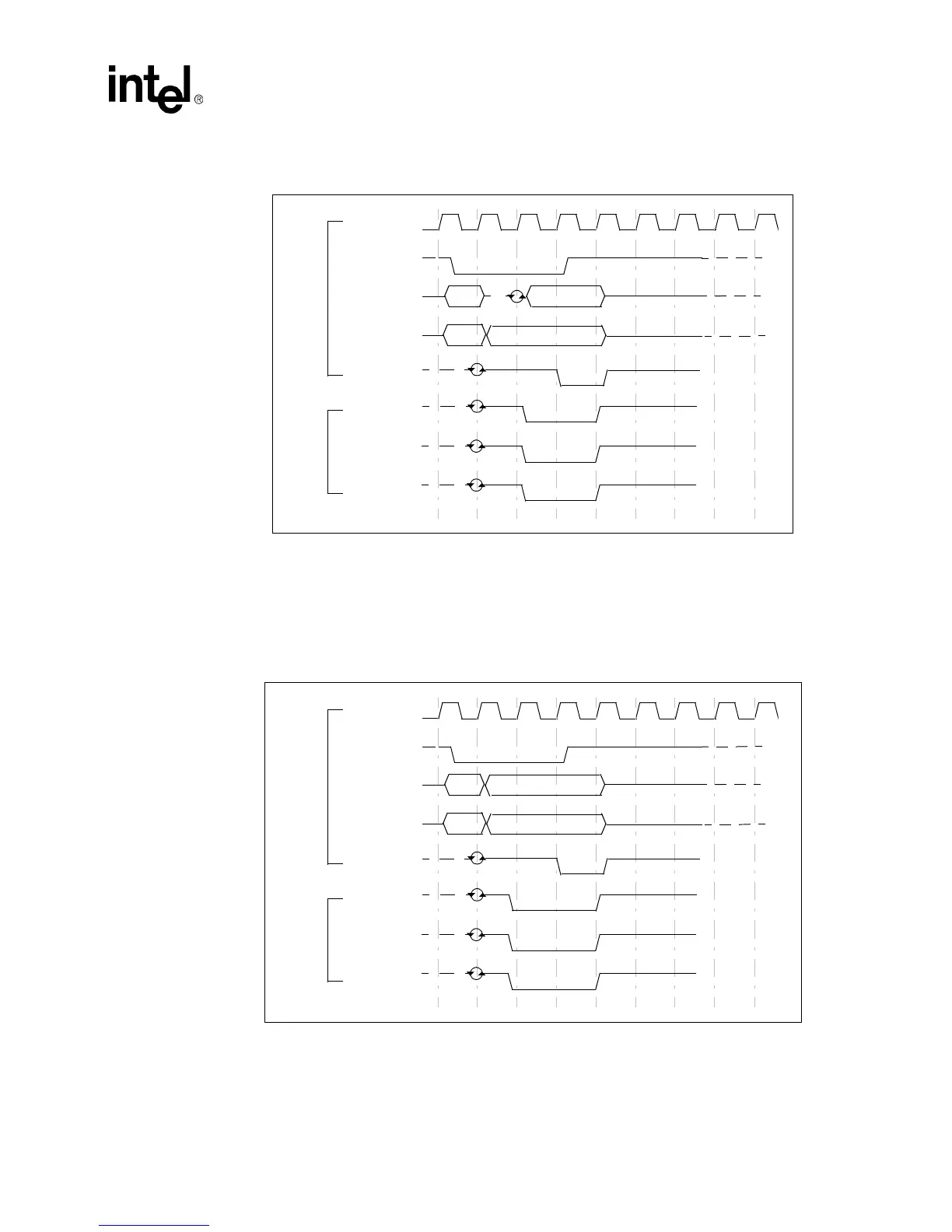

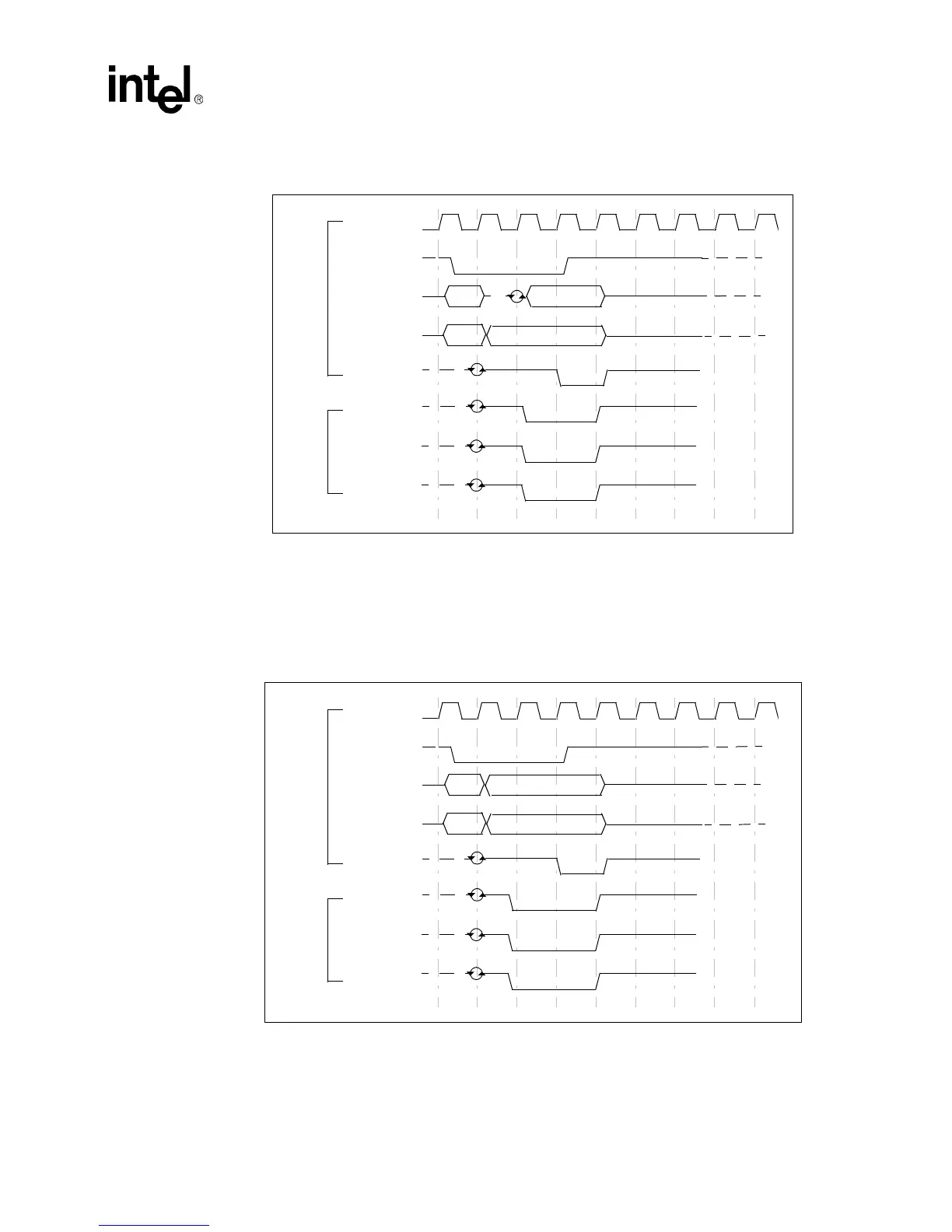

The figures below show CSR zero wait-state I/O read and write cycles. In the case of accessing the

Control/Status Registers, the CPU is the initiator and the 82559ER is the target of the transaction.

Read Accesses:

The CPU, as the initiator, drives address lines AD[31:0], the command and byte

enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. As a slave, the 82559ER

controls the TRDY# signal and provides valid data on each data access. The 82559ER allows the

CPU to issue only one read cycle when it accesses the Control/Status Registers, generating a

disconnect by asserting the STOP# signal. The CPU can insert wait states by de-asserting IRDY#

when it is not ready.

Write Accesses:

The CPU, as the initiator, drives the address lines AD[31:0], the command and

byte enable lines C/BE#[3:0] and the control lines IRDY# and FRAME#. It also provides the

82559ER with valid data on each data access immediately after asserting IRDY#. The 82559ER

Fi

ure 2. CSR I/O Read C

cle

Fi

ure 3. CSR I/O Write C

cle

SYSTEM

82559ER

CLK

FRAME#

C/BE#

IRDY#

TRDY#

DEVSEL#

AD

3421 56789

ADDR

DATA

I/O RD BE#

STOP#

SYSTEM

82559ER

CLK

FRAME#

C/BE#

IRDY#

TRDY#

DEVSEL#

AD

3421 56789

ADDR DATA

I/O WR BE#

STOP#

Loading...

Loading...