XV-SA600BK/XV-SA602SL

42

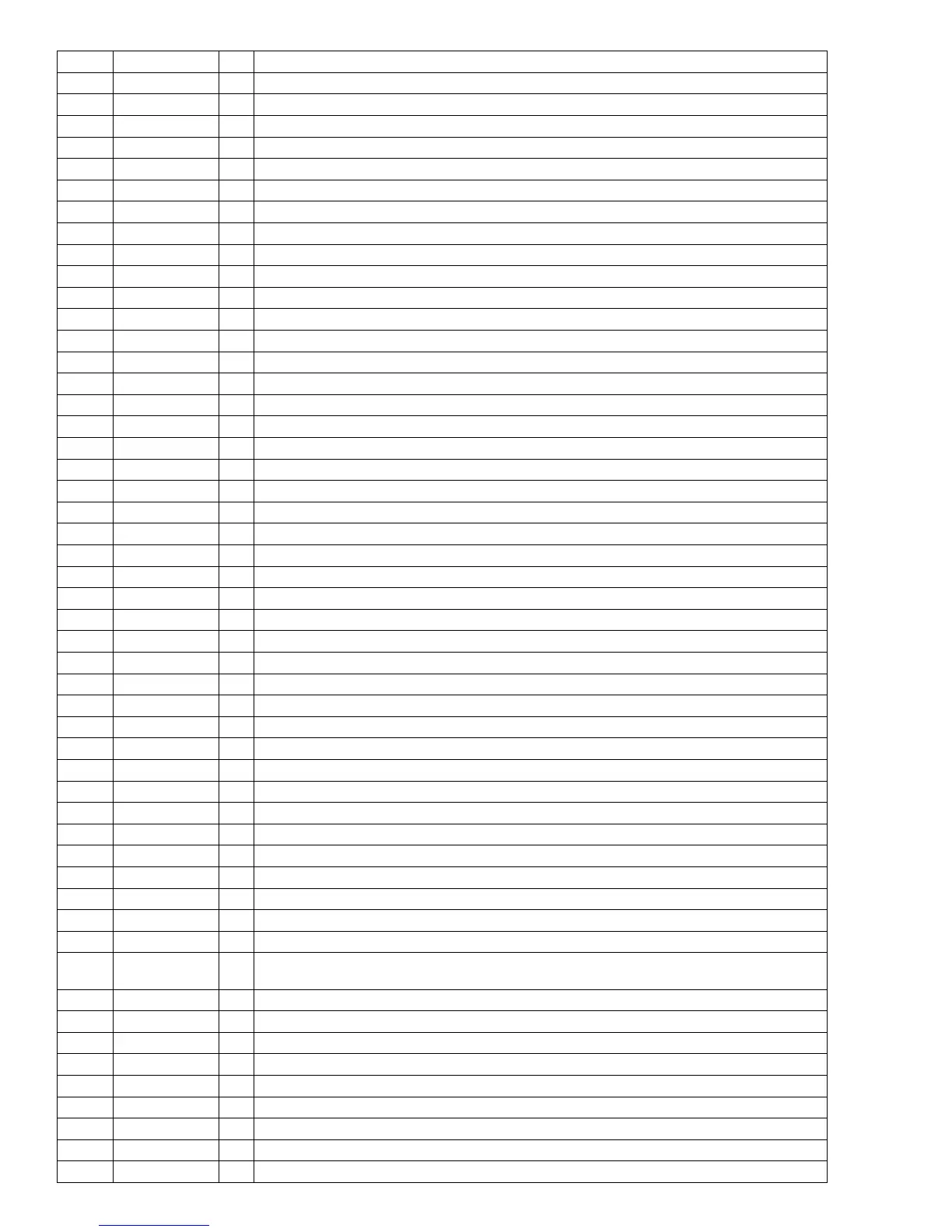

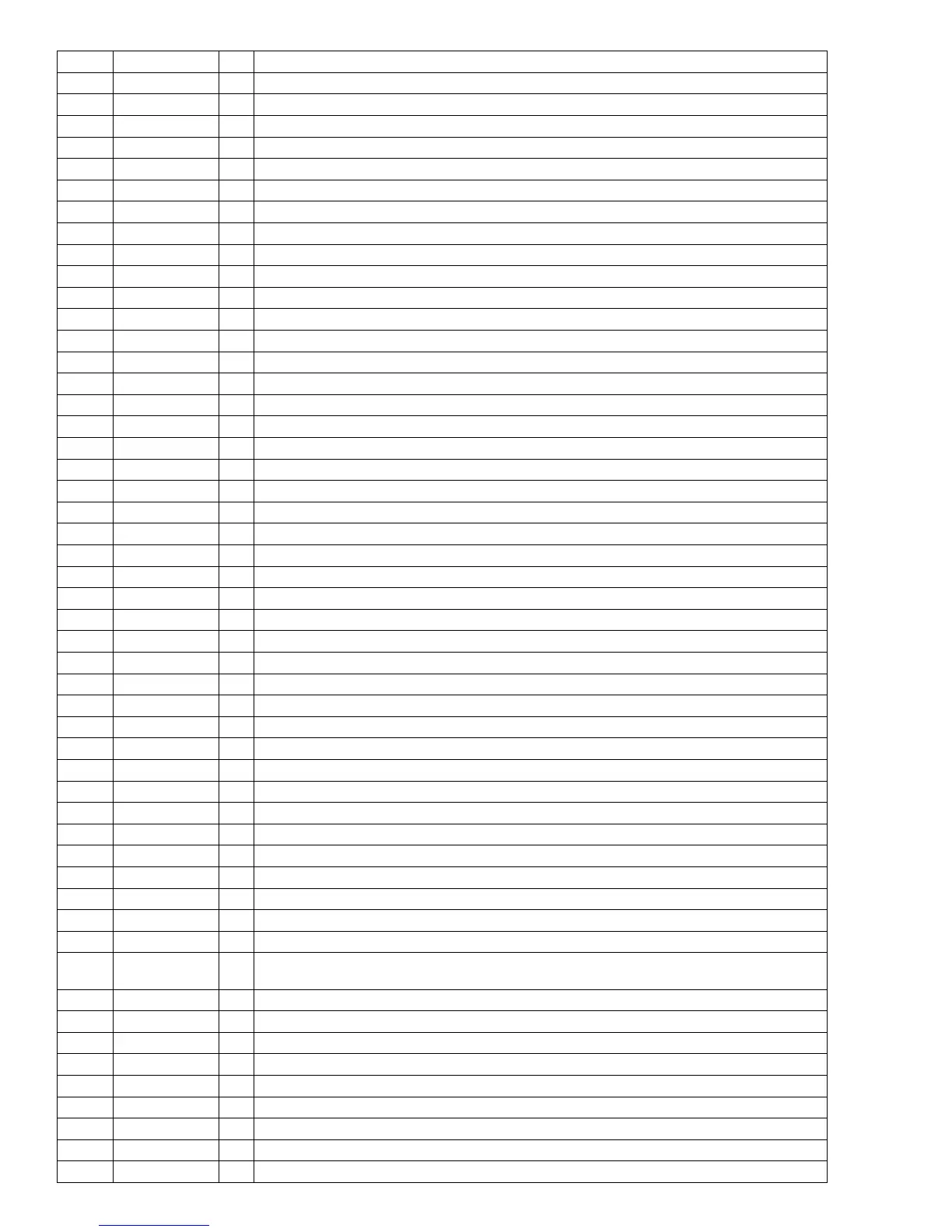

4.12.4 Pin function (NDV8611VWA 2/4)

Pin No. Symbol I/O Description

30 MA11 - Non connect

31 VSSio - Connect to ground

32,33 MA12,13 O SDRAM Address bus, reserved for terminal compatibility with 64Mb SDRAM

34 VDD - Power supply terminal 1.8V

35 CS0 O SDRAM Primary bank chip select

36 VDDio - Power supply terminal 3.3V

37 RAS O SDRAM Command bit

38 CAS O SDRAM Command bit

39 WE O SDRAM Command bit

40 VSSio - Connect to ground

41 DQM0 O SDRAM Data byte enable

42 DQM2 O SDRAM Data byte enable

43 MD16 I/O SDRAM Data bus terminal

44 VDDio - Power supply terminal 3.3V

45,46 MD17,18 I/O SDRAM Data bus terminal

47 VSS - Connect to ground

48 MD19 I/O SDRAM Data bus terminal

49 VSSio - Connect to ground

50~52 MD20~22 I/O SDRAM Data bus terminal

53 VDDio - Power supply terminal 3.3V

54~56 MD23~25 I/O SDRAM Data bus terminal

57 VSSio - Connect to ground

58~61 MD26~29 I/O SDRAM Data bus terminal

62 VDDio - Power supply terminal 3.3V

63,64 MD30,31 I/O SDRAM Data bus terminal

65 DQM3 O SDRAM Data byte enable

66 CS1 O SDRAM Extension bank chip select

67 VSSD - Connect to ground

68 SPDIF O S/PDIF Digital audio output terminal

69 VSSio - Connect to ground

70 AIN I Digital audio input for digital micro; can be used as GPIO

71 AOUT3 O Serial audio output data to audio DAC for left and right channels for down-mix

72 AOUT2 O Serial audio output data to audio DAC for surround left and right channels

73 AOUT1 O Serial audio output data to audio DAC for center and LFE channels

74 AOUT0 O Serial audio output data to audio DAC for left and right channels

75 VDDio - Power supply terminal 3.3V

76 PCMCLK O Audio DAC PCM sampling clock frequency, common clock for DACs and ADC

77 VDD - Power supply terminal 1.8V

78 ACLK O Audio interface serial data clock, common clock for DACs and AD converter

79 LRCLK O Left / right channel clock, common clock for DACs and ADC

80 SRST O Active low RESET signal for peripheral reset

81 RSTP I RESET_Power : from system, used to reset frequency synthesizer and rest

of chip

82 VSSio - Connect to ground

83 RXD1 I UART1 Serial data input from external serial device, used for IR receiver

84 SSPIN1 I/O SSP1 Data in or 16X clock for USART function in UART1

85 VSS - Connect to ground

86 SSPOUT1 I/O SSP1 Data out or UART1 data-terminal-ready signal

87 SSPCLK1 I/O SSP1 Clock or UART1 clear-to -send signal

88 SSPCLK0 I/O SSP0 Clock or request-to-send function in UART1

89 VDD - Power supply terminal 1.8V

90 SSPIN0 I/O SSP0 Data in or 16X clock for USART function in UART0

Loading...

Loading...