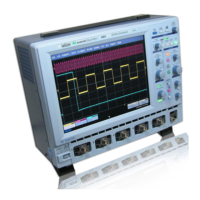

4.6.1.5 Timebase & Trigger

Comprised of ATC FPGA, HTB645, MST429, SDRAM

Trigger Threshold

Generates many system clocks (125MHZ, 500MHz from 10GHz)

Handles Starting and Stopping of ADCs and Memory

Counters for pre and post trigger

TDC for waveform trigger position

Fanout for External Clock

Smart Trigger

Sequence Mode (Time stamp stored in SDRAM)

MST429A

HTB645

External Controls

(DACs, Digital Level Translator)

To & From ATC-uC

Control BUS

Analog controls

(DACs)

Control Bits

Analog controls

(DACs)

Analog Trigger

lines from FE

External CLKs

Digital Trigger

lines from HTB

comparators

Valid

smart trigger

ADC 's

StartStop (1-4)

MACQ (1-8)

MAMClk (1-4)

Ref

Clk

Clocks

Figure 4-6 Trigger and Timebase Block Diagram

4.6.1.5.1 HTB645 – Hybrid Timebase Trigger IC which performs all

standard triggers and control of individual acquisitions by the

ADC and Memory system.

4.6.1.5.1.1 Trigger Bandwidth – The trigger bandwidth of

the system using standard triggers is 5 GHz.

4.6.1.5.1.2 Trigger Signal I/O – There are five differential

trigger inputs, five differential trigger

comparator outputs to be used by an external

Smart Trigger IC, five analog trigger level

threshold control lines, five analog trigger

hysteresis control lines (they are all connected

together in this implementation), five trigger

selection lines and a validate trigger input from

the smart trigger.

Theory of Operation 4-9

Loading...

Loading...