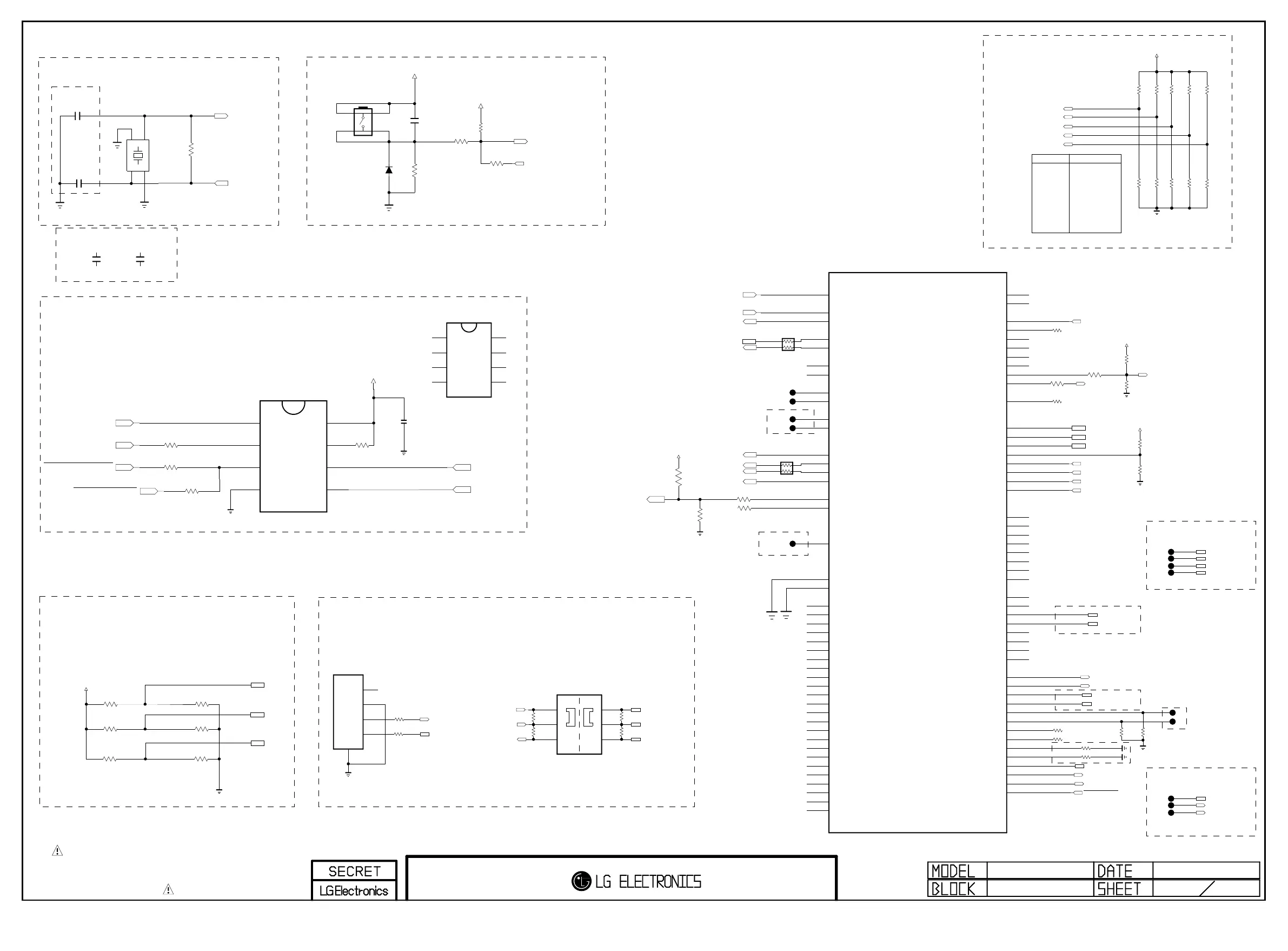

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FIRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFACTURES SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

URSA_BIT1

FRC_FLASH_WP

R13208 33

OPT

R198133

URSA_LOCK_O

SDA2_+3.3V_DB

RXASCL_URSA9

SW1901

JTP-1127WEM

1

2

43

URSA_LOCK_V

Data_Format_1

R1937

10K

SPI_DI

+3.3V_NORMAL

URSA_OPT_1

R1923

10K

R1907

10K

OPT

I2C_SDA1

R1913 10K

URSA_BIT0_1

SPI_CZ

I2C_SCL1

R1933

33

OPT

R13202 33

OPT

R1935

33

DIM1

R1961

0

OPT

R1959

0

URSA_MP

+3.3V_NORMAL

+3.3V_NORMAL

R1925

1M

P1905

12507WS-04L

WAFER-STRAIGHT

URSA_DEBUG

1

2

3

4

5

DIM0

XIN_URSA

URSA9_CONNECT

AR13200

33

D1900

100V

1N4148W

SPI_CK

SW1902

JS2235S

URSA_DEBUG_SW

3

2

1

4

5

6

R1909 10K

URSA_RX_LVDS

DIM1

RXBSDA_URSA9

FLASH_WP_URSA

+3.3V_NORMAL

R1902

10K

R13205

10K

URSA_RESET

FLASH_WP_URSA

R13200

10K

URSA_RX_Vx1_HTPDn

Data_Format_0

URSA_LOCK_O

SPI_CZ

RXBSCL_URSA9

I2CS_SDA

R1912

10K

OS_Module

R1320110K

URSA_RX_Vx1_HTPDn

SDA2_+3.3V_DB

R1934

33

R1936

10K

OPT

SCL2_+3.3V_DB

L_DIM_EN

URSA_LOCK_V

R1958

0

URSA_MP

URSA_RESET

R1924

0

URSA_OPT_0

R1915 10K

URSA_BIT1_1

R190310K

R1954

1K

OPT

SPI_DO

R1905

1K

U_SPI_WP_f_URSA

R1921

33

URSA_DEBUG

R1908

10K

OPT

R1922

33

URSA_DEBUG

URSA_BIT2

RXASDA_URSA9

AR13201

33

SPI_CK

I2CS_SDA

URSA_BIT1

TCON_I2C_EN

I2CS_SCL

DIM2

URSA_BIT0

R1917 10K

URSA_BIT2_1

R1904

33

DIM2

SPI_DI

R1914 10K

URSA_BIT0_0

URSA_OPT_1

XIN_URSA

R1932

1K

U_SPI_WP_f_SoC

I2CS_SCL

DIM0

URSA_BIT2

R13203 33

OPT

R13204

10K

OPT

R1906

10K

OPT

R1916 10K

URSA_BIT1_0

URSA9_CONNECT

C1902

22uF

10V

OPT

R1910 10K

URSA_RX_VX1

R1911

10K

LGD_Module

R1918 10K

URSA_BIT2_0

URSA_RESET_SoC

IC1901-*1

W25Q32BVSSIG

SPI_4MB_Winbond

3

/WP[IO2]

2

DO[IO1]

4

GND

1

/CS

5

DI[IO0]

6

CLK

7

/HOLD[IO3]

8

VCC

X1900

24MHz

4

GND_2

1

X-TAL_1

2

GND_1

3

X-TAL_2

+3.3V_NORMAL

R1900

10K

+3.3V_NORMAL

C1901

0.1uF

16V

+3.3V_NORMAL

R13209

100K

XO_URSA

R13207 33

OPT

R1960

0

OPT

SCL2_+3.3V_DB

XO_URSA

3D_EN

URSA_BIT0

URSA_OPT_0

R1901

10K

SPI_DO

R1955

10K

R1930

0

IC1901

MX25L3206EM2I-12G

SPI_4MB_MACRONIX

3

WP#

2

SO/SIO1

4

GND

1

CS#

5

SI/SIO0

6

SCLK

7

HOLD#

8

VCC

RXASCL_URSA9

RXASDA_URSA9

RXBSCL_URSA9

RXBSDA_URSA9

R13206

100K

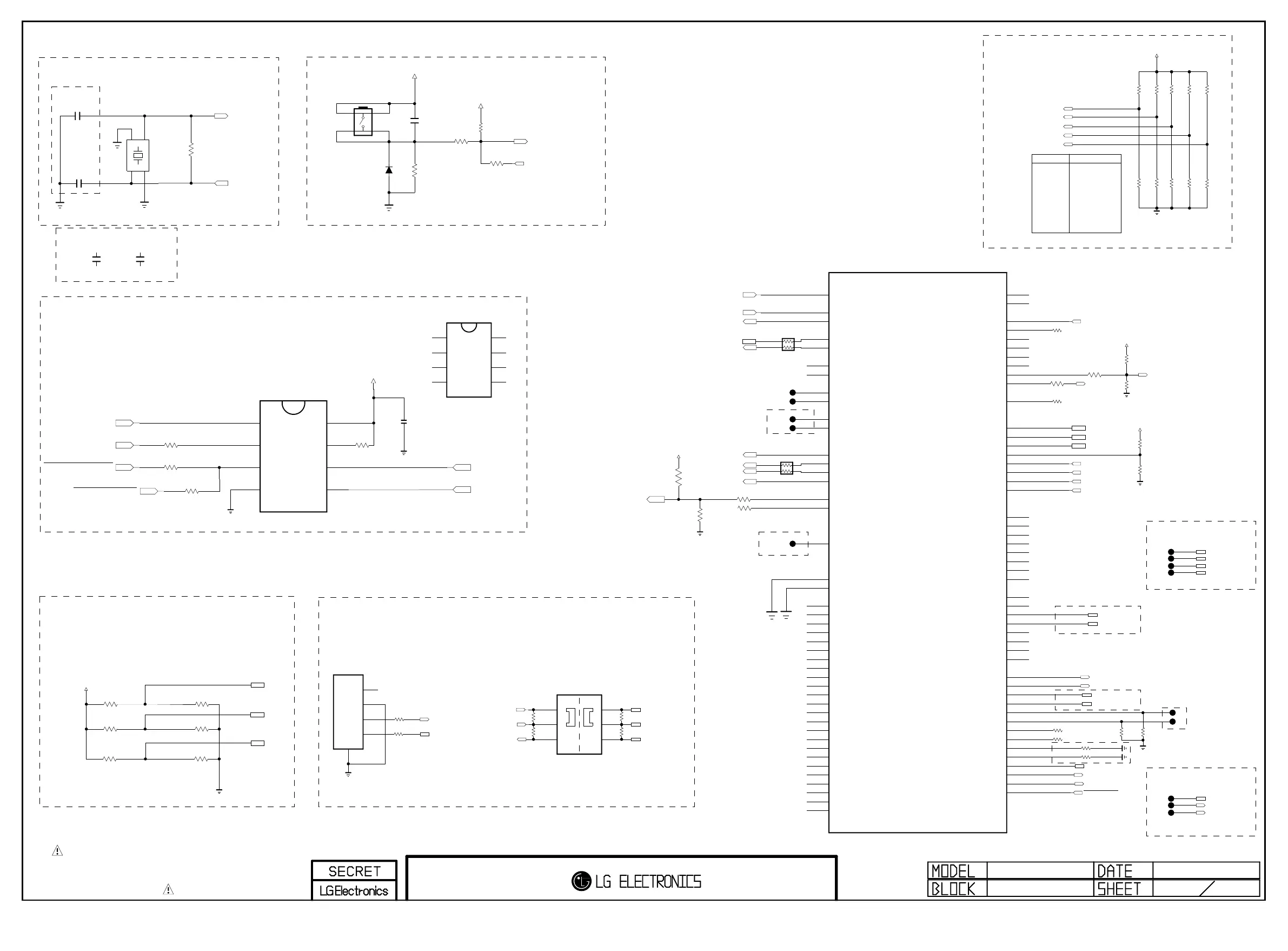

IC2500

LGE7411(URSA9)

RESET

AF29

XTALO

R3

XTALI

R4

I2CS_SDA

AJ24

I2CS_SCL

AH24

I2CM_SDA

AH26

I2CM_SCL/VSYNC_LIKE1

AG24

GPIO[0][UART2_TX]

B4

GPIO[1][UART2_RX]

A4

GPIO[2][UART1_TX]

B5

GPIO[3][UART1_RX]

A5

SPI_CZ

AD28

SPI_CK

AD30

SPI_DI

AC31

SPI_DO

AD29

INT_R21/GPIO[41]

AE28

INT_R20/GPIO[42]

AE27

IRE

C4

GND_1

AC27

GND_2

AD27

NC_1

A7

NC_2

B6

NC_3

B7

NC_4

C5

NC_5

C6

NC_6

C7

NC_7

D4

NC_8

D5

NC_9

D6

NC_10

D7

NC_11

E4

NC_12

E5

NC_13

E6

NC_14

E7

NC_15

F4

NC_16

F5

NC_17

M5

NC_18

M6

NC_19

M7

NC_20

N5

NC_21

R7

NC_22

P7

NC_23

N7

NC_24

N6

I2C_HSC_SDA/VSYNC_LIKE2

AG25

I2C_HSC_SCL/VSYNC_LIKE3

AH25

SPI1_CK/PWM2/GPIO58

AH28

SPI1_DI/PWM3/GPIO59

AJ27

SPI2_CK/PWM0/GPIO56

AJ29

SPI2_DI/PWM1/GPIO57

AF27

SPI3_CK/DIM10/GPIO54

AG28

SPI3_DI/DIM11/GPIO55

AH27

SPI4_CK/DIM8/GPIO52

AG27

SPI4_DI/DIM9/GPIO53

AG26

VSYNC_LIKE/PWM5/GPIO40

AF28

DIM0/GPIO[32]

AG23

DIM1/GPIO[33]

AG20

DIM2/GPIO[34]

AH23

DIM3/GPIO[35]

AH20

DIM4/GPIO[36]

AG21

DIM5/GPIO[37]

AH22

DIM6/GPIO[38]

AG22

DIM7/GPIO[39]

AH21

GPIO43/TCON0

A3

GPIO44/TCON1

B3

GPIO45/TCON2

A2

GPIO46/TCON3

C3

GPIO47/TCON4

B2

GPIO48/TCON5

B1

GPIO49/TCON6

C2

GPIO50/TCON7

C1

GPIO[18]/TCON8

AG4

GPIO[19]/TCON9

AG5

GPIO[20]/TCON10

AH4

GPIO[21]/TCON11

AH5

GPIO[22]/TCON12

AH6

GPIO[23]/TCON13

AJ4

GPIO24/TCON14

AJ5

GPIO25/TCON15

AJ6

GPIO[4]

AH16

GPIO[5]

AG16

GPIO[6]

Y5

GPIO[7]

Y4

GPIO[8]

AB4

GPIO[9]

AB5

GPIO[10]/PWM_DIM_IN[0]

AG17

GPIO[11]/PWM_DIM_IN[1]

AH17

GPIO[12]

AG18

GPIO[13]

AJ20

GPIO[14]

AH18

GPIO[15]

AG19

GPIO[16]

AH19

GPIO[17]

AJ21

C1903

5pF

50V

C1904

5pF

50V

C1903-*1

8pF

50V

C1904-*1

8pF

50V

+3.3V_NORMAL

R1919

10K

URSA9_RST_PULLUP

Slave (Debug Port:0XB4,ISP:0X98)

SPI Flash

0/1/0

Not Used Net (UB85/95/UC89)

Chip Config

0/0/0

BIT [2/1/0]

Debugging for URSA9

Module Type

URSA9_Vx1_RX_HTPD_GPIO

Rx Interface

1/0/0

0/0/1

Tx Lane

FHD@60 (2lane)

1/1/0

CHIP_CONF=3’d7:111:boot from SPI Flash

URSA Reset

Reserved

Reserved

URSA Option

5k@120 (20lane)

0/1/1

Debug/ISP ADDR

For DFT JIG

FHD@120 (4lane)

4k@60 (8lane)

Clock for URSA9

1/1/1

HDMI OUTPUT_1 DDC to URSA9

CHIP_CONF:{DIM2,DIM1,DIM0}

4K@120 (16lane)

I2C_S Port

Tx Lane

HDMI OUTPUT_0 DDC to URSA9

1/0/1

Not Used Net (UB98/D9)

BSD-14Y-UD-132-HD

2013.12.17

URSA9 UART1_RX

Change pin from A5 to C4

OLED ULTRA HD

Option Name

UB85/95/UC97_URSA9_crystalcap

Option Name

UB98/UC9_URSA9_crystalcap

Copyright ⓒ 2014 LG Electronics. Inc. All right reserved.

Only for training and service purposes

Loading...

Loading...