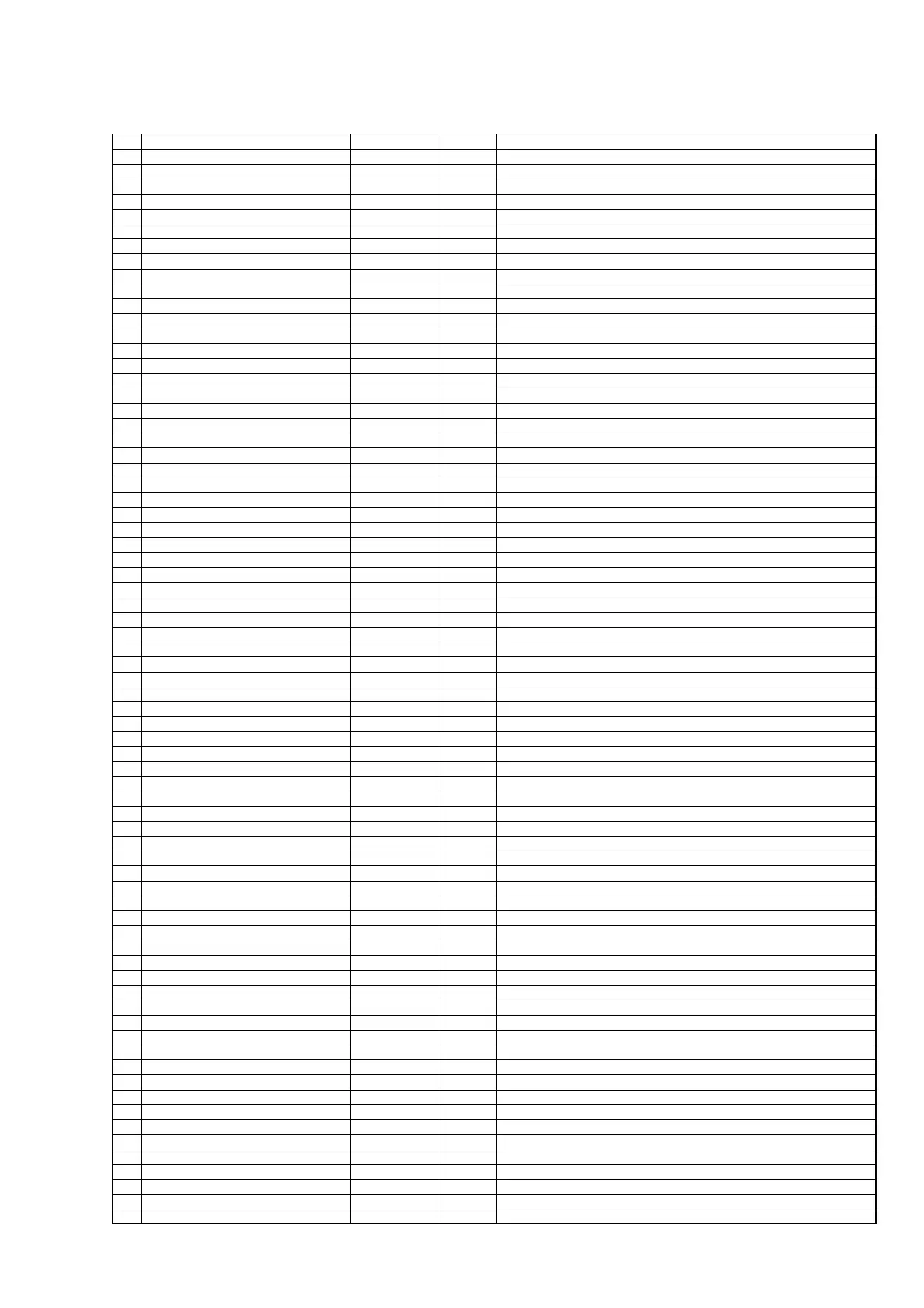

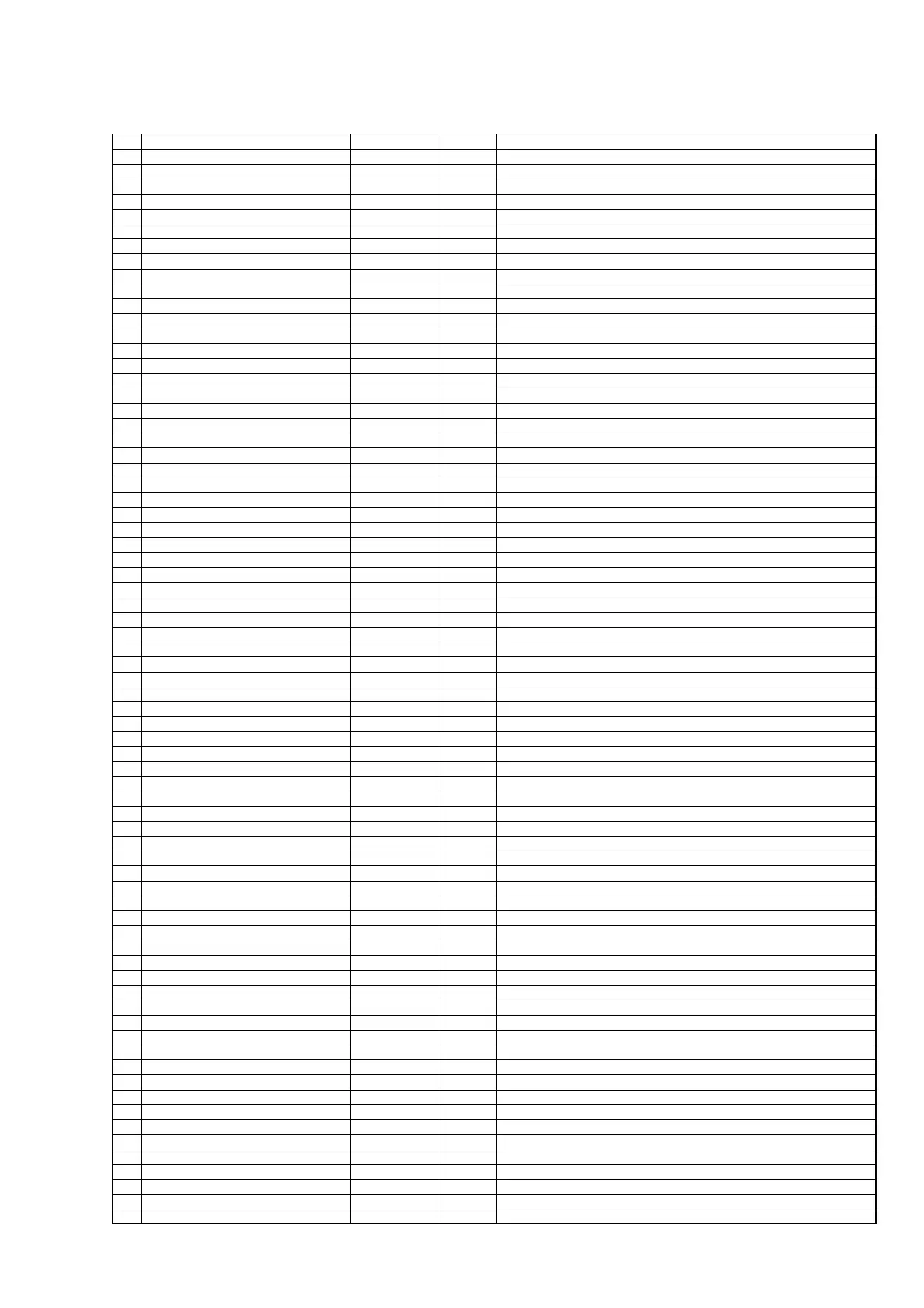

[PM01] Q102(Back End microprocessor) : M32102S6FP

Pin PORT SIGNAL NAME I/O DESCRIPTION

1 SBI# --- I PULL UP

2 DBI# DBI I JTAG

3 TDO TDO O JTAG

4 TDI TDI I JTAG

5 TMS TMS I JTAG

6 TCK TCK I JTAG

7 TRSYNC# N.C. O

8 EVENT1 N.C. O

9 EVENT0 N.C. O

10 VSS GND

11 BCLK N.C. O

12 VCCX +3.3V

13 MODE1 --- I PULL UP

14 MODE0 --- I GND

15 TRST# MC_TRST I JTAG

16 RESET# MC_RST I Reset signal for the microprocessor. RESET=L

17 VCC +2.5V

18 XIN 27MHz I System clock input (27MHz)

19 VSS GND

20 XOUT N.C. O System clock output. (27MHz)

21 PLLVCC +2.5V Power supply for PLL.

22 PLLCAP --- I Filter for PLL.

23 PLLVSS GND GND for PLL

24 P56/SCLK1 DRVCLK O Clock output to CXD1185.

25 P54/TXD1 DRVRX O Serial data output to CXD1185.

26 P55/RXD1 DRVTX

I Input serial data from CXD1185.

27 VCCX +3.3V

28 TEST GND

29 TRCLK N.C. O

30 VSS GND

31 P57/CTS1#/RTS1# DRVRDY I Ready signal from CXD1185. Ready=L

32 P52/SCLK0 CLK_OP O Clock output for serial transmission to panel microprocessor.

33 TRDATA0 N.C. O

34 P50/TXD0 DATAI_OP O Serial data output to panel microprocessor.

35 P51/RXD0 DATAO_OP I Serial data input from panel microprocessor.

36 P53/CTS0#/RTS0# CS_OP O Chip select output to panal microprocessor.

37 P71/INT0 DRVIRQ I The interruption demand from CXD1185. Interruption=L

38 P72/INT1 MC_INTR I The interruption demand from M65776. Interruption=L

39 P73/INT2 MC_INT2 I The interruption demand from M65776. Interruption=L

40 TRDATA1 N.C. O

41 P74/INT3 SVA_INT3 I The interruption demand from M65776. Interruption=L

42 VCCX +3.3V

43 VSS GND I

44 P75/INT4/MFT0A/MFT2B SELDSD O DSD selection output. DSD=H

45 P76/INT5/MFT1A/MFT0B DSDRST O Reset signal for the CXD2753. RESET=L

46 TRDATA2 N.C. O

47 P77/INT6/MFT2A/MFT1B V_CONT O Tray control output. (PWM)

48 TRDATA3 N.C. O

49 D31/P47 N.C. O

50 D30/P46/RTS4# N.C. O

51 D29/P45/CTS4# MSREADY I Ready signal output to CXD2753. Completion=L

52 VCC +2.5V

53 D28/P44/SCLK4 MSCK O Clock output to CXD2753.

54 VSS GND

55 D27/P43/RXD4 MSDATAO I Data input from CXD2753.

56 D26/P42/TXD4 MSDATAI O Data output to CXD2753.

57 D25/P41/RTS3# V_SDA I/O IIC data.

58 D24/P40/CTS3# V_SCL O IIC cloc

59 TRDATA4 N.C. O

60 TRDATA5 N.C. O

61 TRDATA6 N.C. O

62 VCCX +3.3V

63 TRDATA7 N.C. O

64 D23/P37/SCLK3 N.C. O

65 D22/P36/RXD3 SMUTE O MUTE for CXD2753. MUTE ON=H

66 D21/P35/TXD3 N.C. O

67 D20/P34/RTS2# --- I PULL DOWN

68 D19/P33/CTS2#

DFRES O Initialization on a panel microprocessor. Completion=L

69 D18/P32/SCLK2 XMSLAT O Latch output to CXD2753•

70 D17/P31/RXD2 CDDA O Select CDDA direction. Direct=H

71 VSS GND

72 D16/P30/TXD2 B/EON O B/E state Standby=L, Power ON=H

155

Loading...

Loading...