dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 12 2018 Microchip Technology Inc.

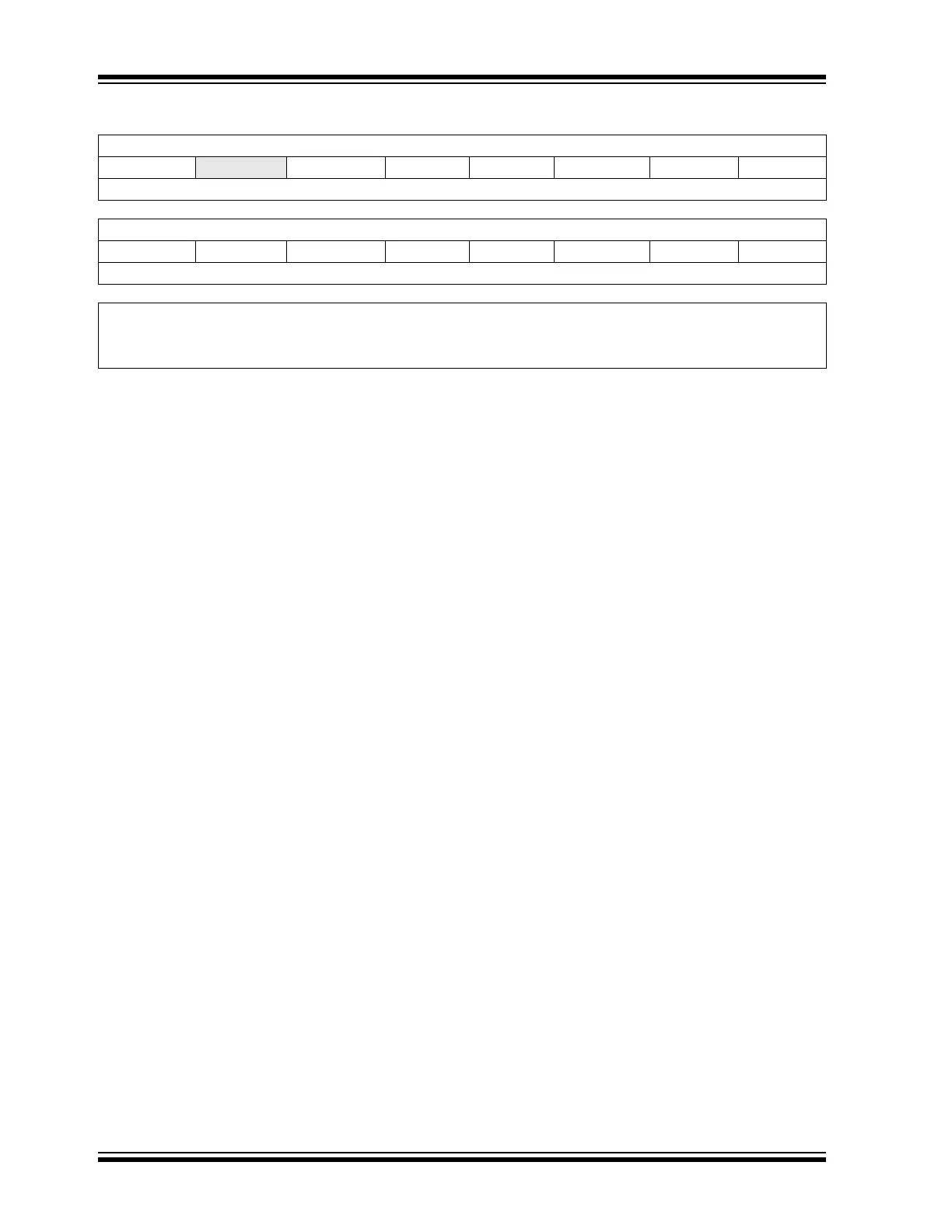

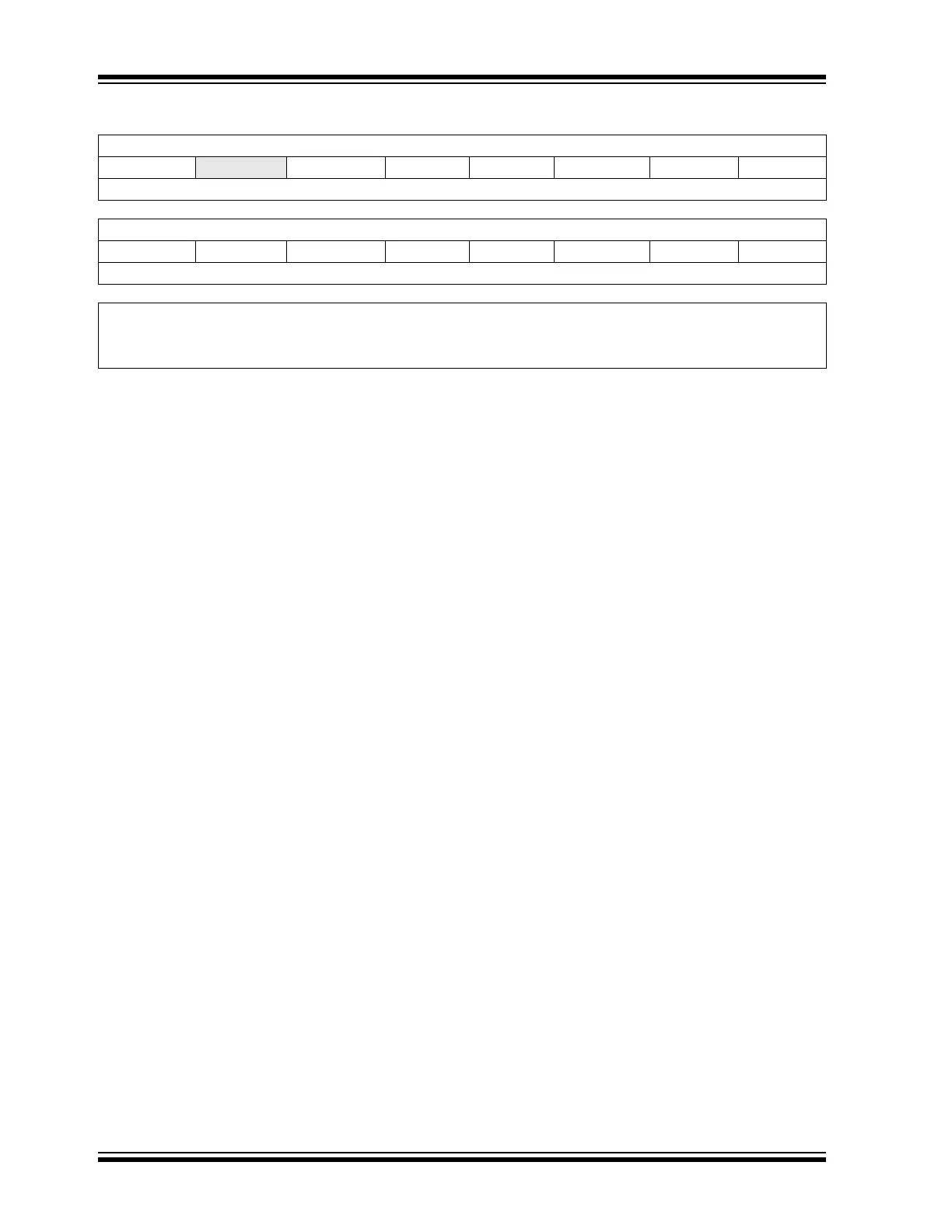

Register 3-2: C1CONL: CAN Control Register Low

R/W-0 U-0 R/W-0 R/W-0 R-0 R/W-1 R/W-1 R/W-1

CON

— SIDL BRSDIS BUSY WFT1 WFT0 WAKFIL

(1)

bit 15 bit 8

R/W-0 R/W-1 R/W-1 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

CLKSEL

(1)

PXEDIS

(1)

ISOCRCEN

(1)

DNCNT4 DNCNT3 DNCNT2 DNCNT1 DNCNT0

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15 CON: CAN Enable bit

1 = CAN module is enabled

0 = CAN module is disabled

bit 14 Unimplemented: Read as ‘0’

bit 13 SIDL: CAN Stop in Idle Control bit

1 = Stops module operation in Idle mode

0 = Does not stop module operation in Idle mode

bit 12 BRSDIS: Bit Rate Switching Disable bit (BRS)

1 = Bit Rate Switching is disabled, regardless of BRS in the transmit message object

0 = Bit Rate Switching depends on BRS in the transmit message object

bit 11 BUSY: CAN Module is Busy bit

1 = The CAN module is active

0 = The CAN module is inactive

bit 10-9 WFT<1:0>: Selectable Wake-up Filter Time bits

11 = T11

FILTER

10 = T10

FILTER

01 = T01

FILTER

00 = T00

FILTER

bit 8 WAKFIL: Enable CAN Bus Line Wake-up Filter bit

(1)

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 7 CLKSEL: Module Clock Source Select bit

(1)

1 = Auxiliary clock is active when module is enabled

0 = CAN clock is not active when module is enabled

bit 6 PXEDIS: Protocol Exception Event Detection Disabled bit

(1)

A recessive “reserved bit” following a recessive FDF bit is called a “Protocol Exception”.

1 = Protocol exception is treated as a form error

0 = If a protocol exception is detected, CAN will enter the bus integrating state

bit 5 ISOCRCEN: Enable ISO CRC in CAN FD Frames bit

(1)

1 = Includes stuff bit count in CRC field and uses non-zero CRC initialization vector

0 = Does not include

Stuff Bit Co

unt in CRC field and uses CRC initialization vector with all zeros

bit 4-0 DNCNT<4:0>: DeviceNet™ Filter Bit Number bits

10011-11111 = Invalid selection (compares up to 18 bits of data with EIDx)

10010 = Compares up to DATA Byte 2, bit 6 with EID17

...

00001 = Compares up to Data Byte 0, bit 7 with EID0

00000 = Does not compare data bytes

Note 1: These bits can only be modified in Configuration mode (OPMOD<2:0> =

100

).

Loading...

Loading...