TP LOOP Black

DNP

TP5

1

2

J10

Pole at ~ 15.9 kHz (J10 Open)

Pole at ~ 1.45 kHz (J10 Closed)

10 μF

25V

0805

C34

10 μF

25V

0805

C35

R S X 1 0 1 MM- 30 T R

D5

10 μF

25V

0805

C36

4.7k

1%

R70

4.7k

1%

R80

Resistor Gain (J13 Closed) = 0.5481 (1.470 mV/ADC LSB at 12-bit, 3.3 VREF)

1k

1%

R57

VOUT_FB

1

2

J13

1k

0603

1%

R72

Resistor Gain (J13 Open) = 0.1754 (4.592 mV/ADC LSB at 12-bit, 3.3 VREF)

3V3

100R

0603

1%

R55

1k

0603

1%

R85

470R

0603

1%

R83

1k

0603

1%

R79

1

3

2

MMBT3904

Q9

100R

0603 1%

R87

S1PWM2L_DAC_ISET

VOUT

0.010 μF 25V

0603

C40

2.2k

0603

1%

R84

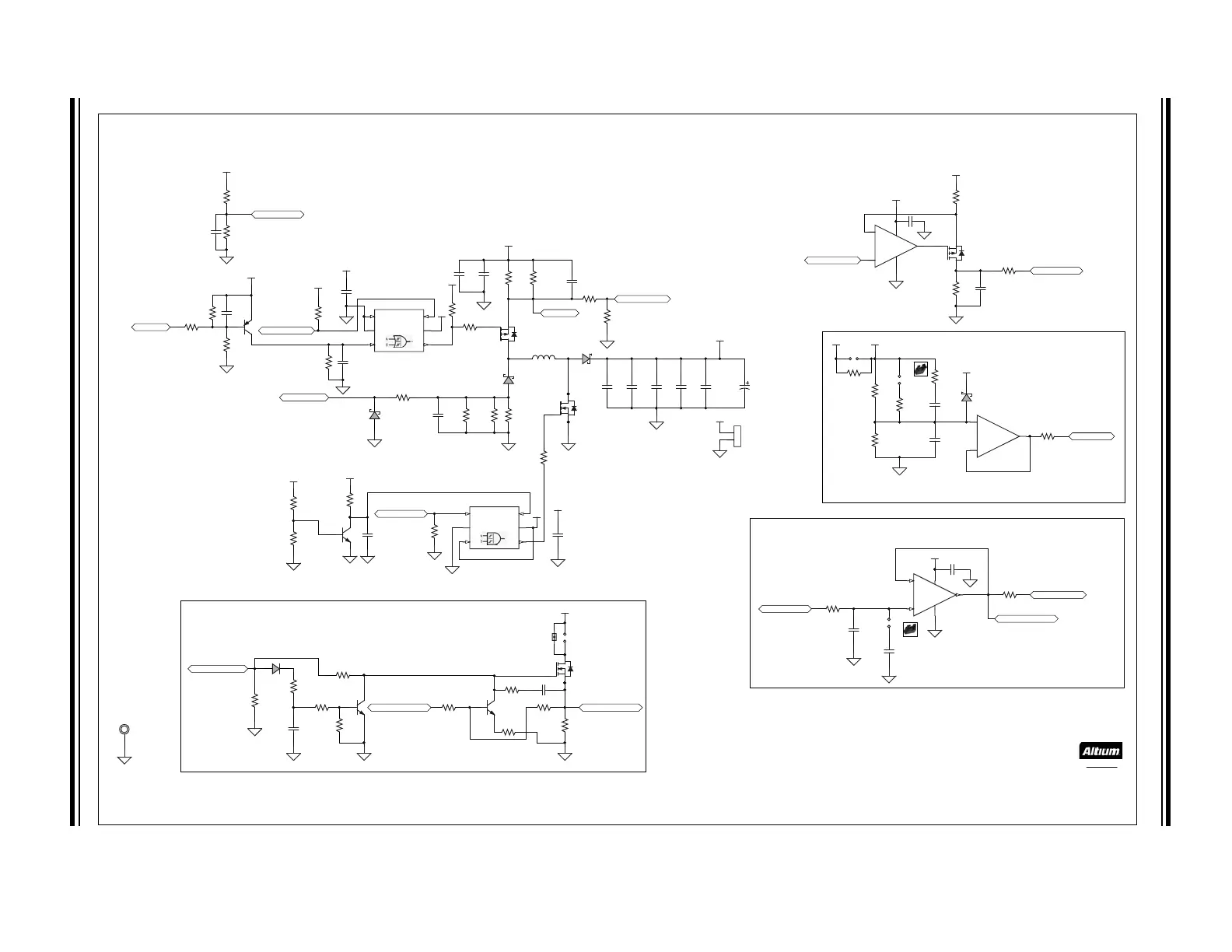

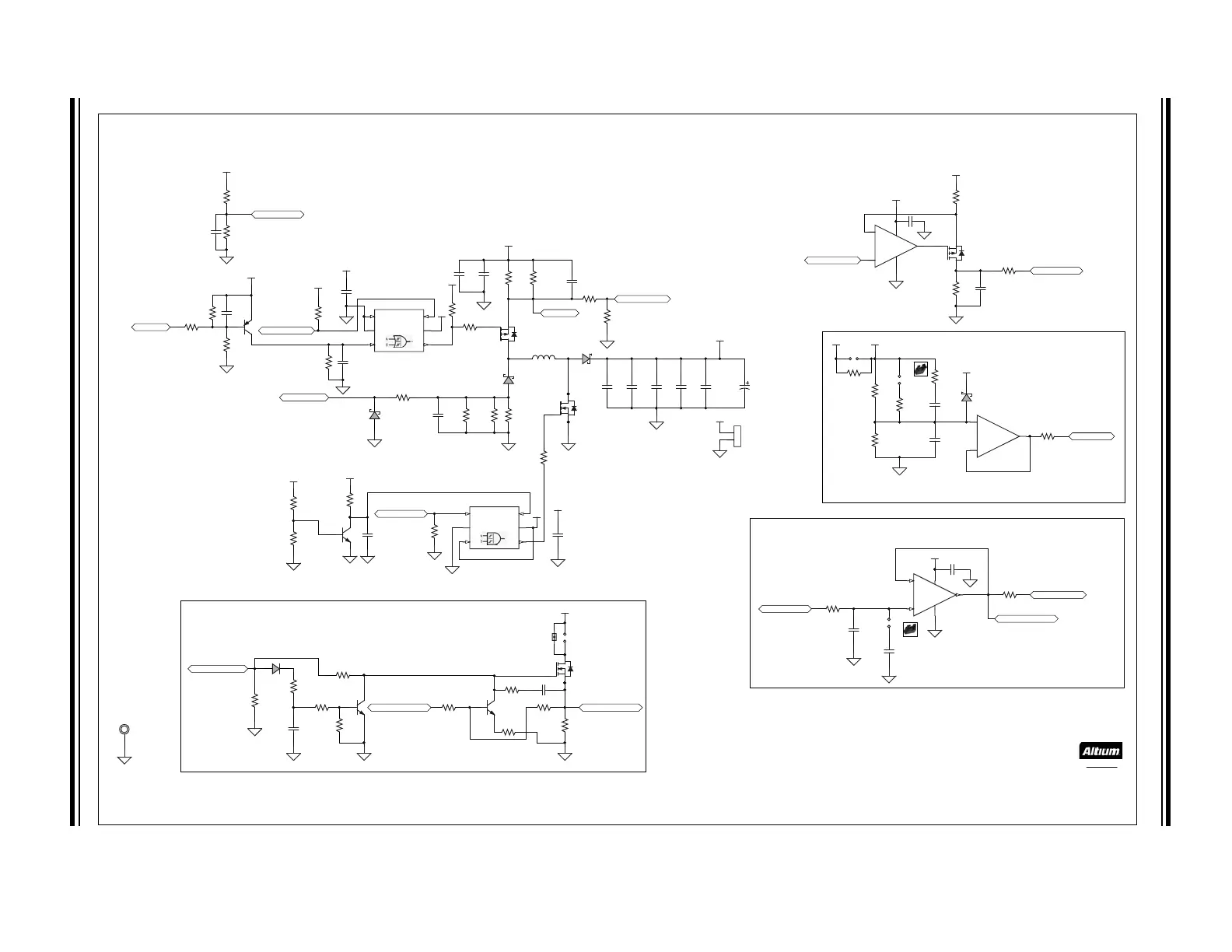

S1PWM2L DAC/DC Bias Generator/RC Filter

On-time restrictor

sub-circuit

Adjustable constant-current transient load

Note: Q8 is driven in the linear region.

Limit (peak power) * (on-time) product to

maintain peak Q8 juntion temp <150°C.

0.010 μF

25V

0603

C26

4

1,2,3

5,6,7,8

MCP87130T

Q8

1

3

2

MMBT3904

Q10

10k

1%

R88

20k

0603

1%

R90

20k

0603

1%

R91

MMBD914

D6

10k

1%

R89

Transient Load Tester Circuit

1R

1206

1%

1/4W

R94

1R

1206

1%

1/4W

R9 3

1R

1206

1%

1/4W

R9 2

1R

1206

1%

1/4W

R59

1R

1206

1%

1/4W

R74

10 μF

25V

0805

C42

DNP

C44

DNP

C43

DNP

R86

0603

DNP

C3 8

100R

0603

1%

R9 5

0.1 μF

25V

C25

0.1 μF 25V

0603

C37

0.1 μF

25V

0603

C41

16V

1 μF

0603

C51

100R

0603

1%

R52

330R

1%

R98

DNP

C46

470R

0603

1%

R103

0603

DNP

C52

100R

0603

1%

R61

High-side current sense level shifter

Output voltage feedback circuit

Buck mode low-side o-time current

sense (Note: 0.0V to -300 mV signal,

suggest -8x PGA gain)

For Buck Mode: PWM Q6, Drive Q2 DC OFF

For Boost Mode: Drive Q6 DC OFF (logic high or tri-state), PWM Q2

For Buck/Boost Mode: PWM Q6 and Q2 with s ame s

ignal

(Note: Q6 drive should be active-low, Q2 active-high)

Congurable Buck, Boost or Buck/Boost Test Circuit

Input voltage mo nitoring

4

1,2,3

5,6,7,8

MCP87130T

Q2

3V3

0R

0603

R60

+A

3

-A

2

OUTA

1

MCP6292

U7B

BAT54

D8

1

3

2

MMBT3904

Q7

VOUT

0.010 μF

25V 0603

C15

10k

1%

R65

270R

1%

R66

0.010 μF

25V

0603

C22

20k

0603

1%

R67

1

2

3

MMBT3906

Q11

5V

1k

0603

1%

R68

DNP

C45

DNP

R71

DNP

R69

Hardware overcurrent

protection (useful during

firmware development)

Output overvoltage protection (useful

during firmware development)

ISE NSEH

10 μF

25V

0805

C47

VOUT

GND

2

I0

3

Y

4

Vcc

5

I2

6

I1

1

NC7SZ58P6X

U10

5V

Configure d a s : Sc hmitt OR

C onfigured as: Schmitt AND

3

1

2

RZM001P02T2L

Q1

GND

2

I0

3

Y

4

VCC

5

I2

6

I1

1

NC7SZ57P6X

U5

3V3

3V3

ISE NSEH_BIASED

RD14_ISENSEL

RA3_ISENSEH

RA1_VINSENSE

RA2_TRANSIENTFB

12

DNP

J19

5V

RC14_S 1PWM7H

820R

1%

R58

RC5_S1PWM2L

S1 P W M 2 L _ DA C _ I S E T

RC13_T RANSIENT

RC0_PWMDACFB

VOUT

Net T ie

NT5

1

2

DNP

J14

R SX101MM-30TR

D2

10 μF

25V

0805

C53

10 μF

25V

0805

C55

10k

1%

R82

5V

1 2

TERMINAL 1x2

J21

VOUT

20R

0805

1%

R96

10k

1%

R102

150R

0603

1%

R97

ISE NSEH_BIASED

ISE NSEH

10k

1%

R64

RC1_VOUTFB

0.010 μF

25V

0603

C54

100 μF

25V

C57

Low ESR

Scre w

3

1

2

BSS30 8PE

Q6

33 μH

L1

Loading...

Loading...