PICkit™ 3 Starter Kit User’s Guide

DS41628B-page 86 2012 Microchip Technology Inc.

3.13.5 New Registers

3.13.5.1 ENHANCED MID-RANGE

Flash program memory is also writable during normal operation. This is commonly

referred to as “Self-modifying code” or “Self-write”. This is achievable by implementing

a modified Harvard architecture.

3.13.5.1.1 EEADRx/EEDATx

When accessing the program memory block, the EEDATH:EEDATL register pair forms

a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH

registers form a 2-byte word that holds the 15-bit address of the program memory loca-

tion being accessed.

3.13.5.1.2 EECON1

Control bit EEPGD determines if the access will be a program or data memory access.

When clear, any subsequent operations will operate on the EEPROM memory. When

set, any subsequent operations will operate on the program memory. On Reset,

EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be

cleared, only set, in software. They are cleared in hardware at completion of the read

or write operation. The inability to clear the WR bit in software prevents the accidental,

premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN

bit is clear.

3.13.5.2 PIC18

3.13.5.2.1 TBLPTR

The Table Pointer (TBLPTR) points to a byte address in program space. Executing

TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified

automatically for the next table read operation.

The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table

Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL).

These three registers join to form a 22-bit wide pointer.

3.13.5.2.2 TABLAT

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table

Latch register is used to hold 8-bit data during data transfers between program memory

and data RAM.

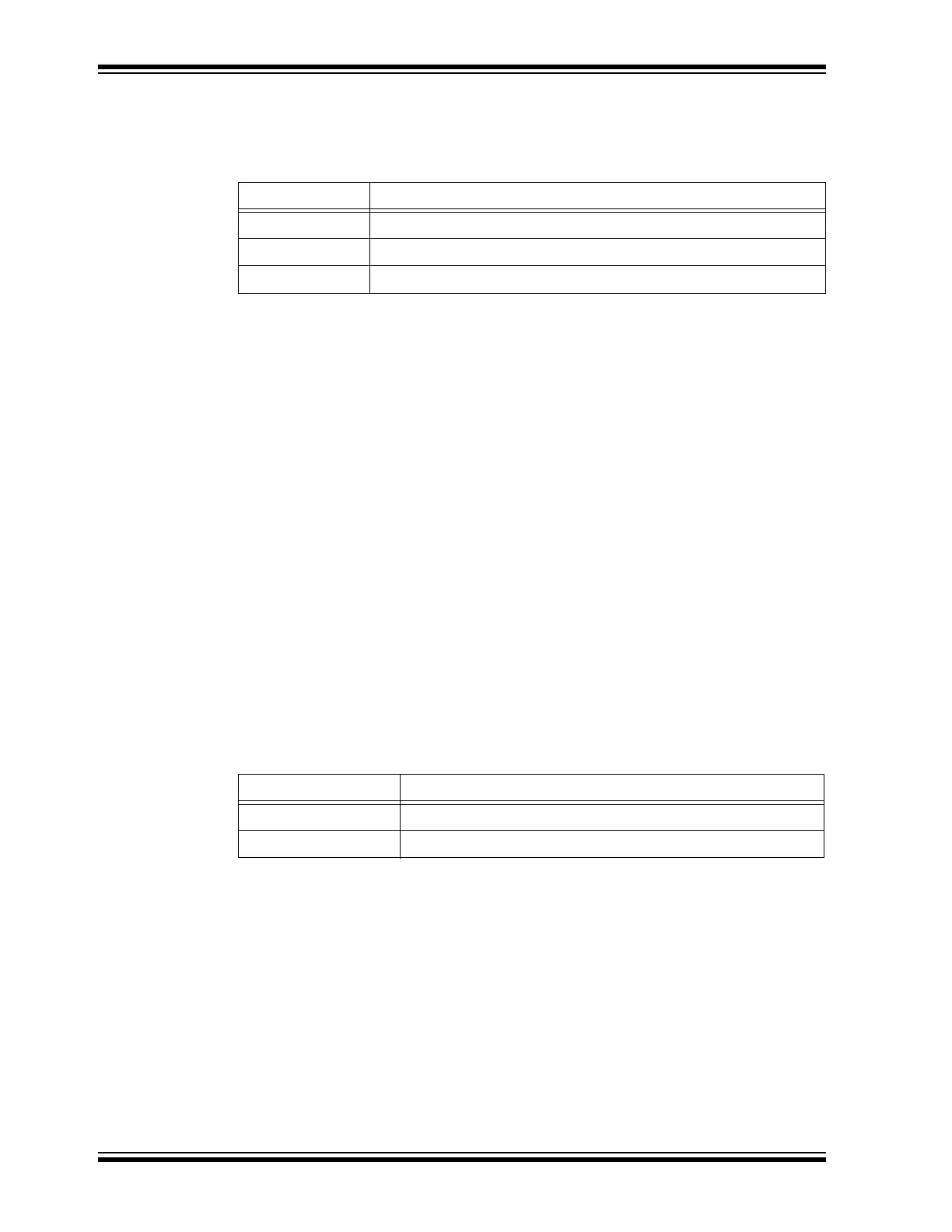

TABLE 3-39: NEW REGISTERS FOR ENHANCED MID-RANGE

Register Purpose

EEADRx Address to read/write in program or EEPROM memory

EEDATx 2-byte word that holds 14-bit data for read/write

EECON1 Control register for memory access

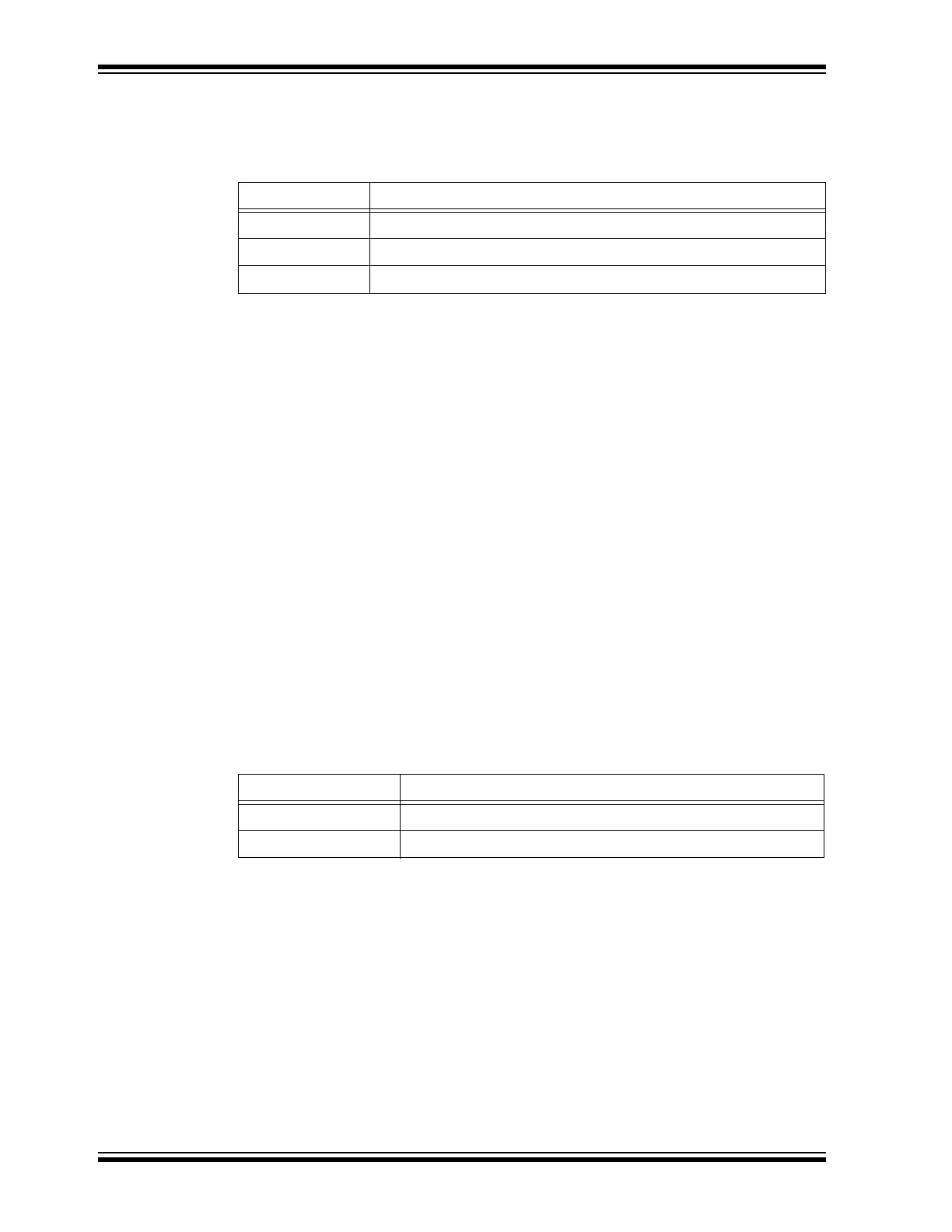

TABLE 3-40: NEW REGISTERS FOR PIC18

Register Purpose

TBLPTR Points to a byte address in program space

TABLAT Holds 8-bit data from program space

Loading...

Loading...