Chapter 3

3-20

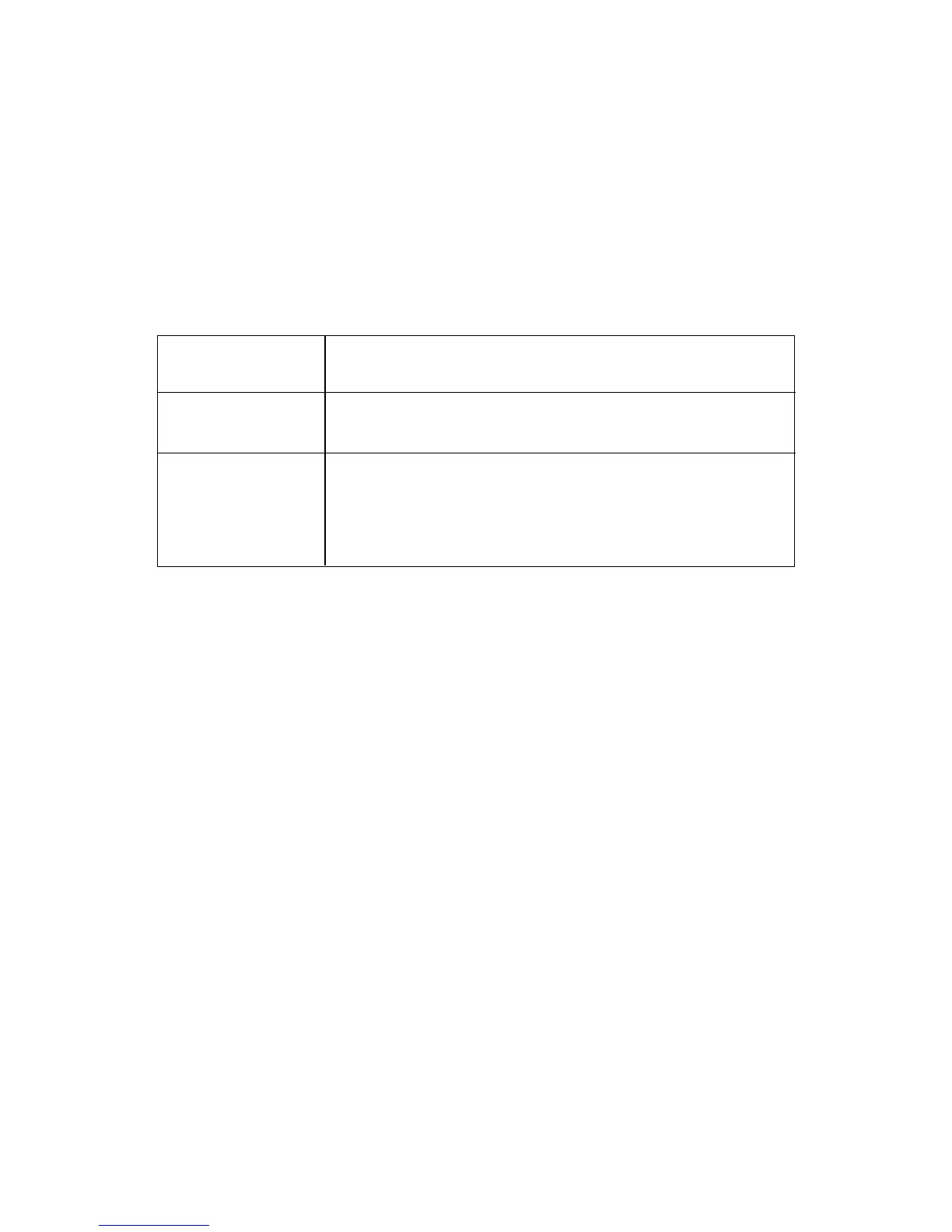

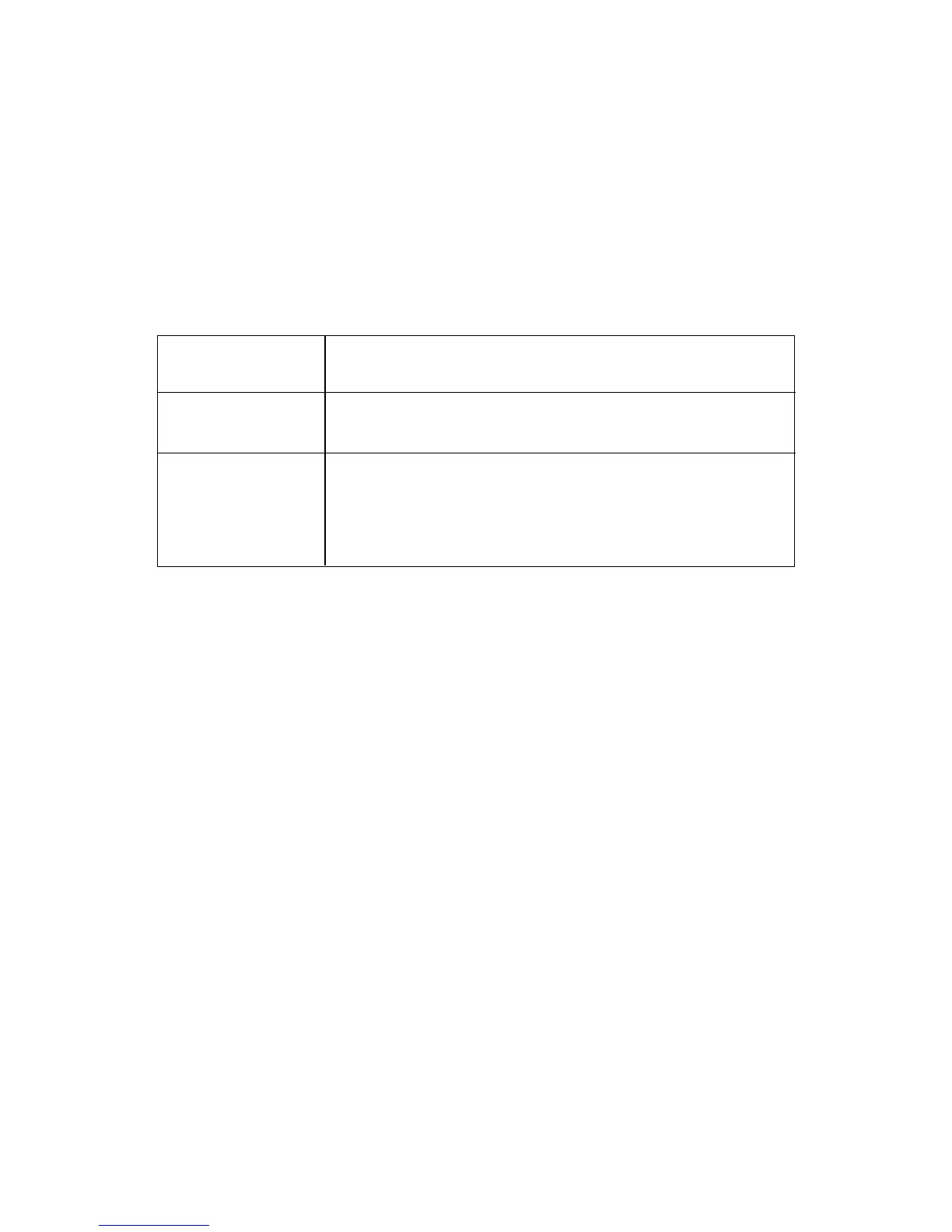

PCI VGA Palette Snoop

When set to Enabled, multiple VGA devices operating on different buses

can handle data from the CPU on each set of palette registers on every video

device. Bit 5 of the command register in the PCI device configuration space

is the VGA Palette Snoop bit (0 is disabled). For example, if there are two

VGA devices in the computer (one PCI and one ISA) and the:

DMA Channel 0/1/3/5/6/7

These items specify the bus that the system DMA (Direct Memory Access)

channel is used. The settings determine if AMIBIOS should remove a DMA

from the available DMAs passed to devices that are configurable by the

system BIOS. The available DMA pool is determined by reading the ESCD

NVRAM. If more DMAs must be removed from the pool, the end user can

reserve the DMA by assigning an ISA/EISA setting to it. The default value

is PnP.

IRQ 3/4/5/7/9/10/11/14/15

These items specify the bus where the specified IRQ line is used. The

settings determine if AMIBIOS should remove an IRQ from the pool of

available IRQs passed to devices that are configurable by the system BIOS.

The available IRQ pool is determined by reading the ESCD NVRAM. If more

IRQs must be removed from the IRQ pool, the end user can use these

settings to reserve the IRQ by assigning an ISA/EISA setting to it. Onboard

I/O is configured by AMIBIOS. All IRQs used by onboard I/O are

configured as PCI/PnP. If all IRQs are set to ISA/EISA, and IRQ 14/15 are

allocated to the onboard PCI IDE, IRQ 9 will still be available for PCI and PnP

devices. Settings are ISA/EISA and PCI/PnP. The default value is PCI/PnP.

VGA Palette Snoop

Bit Setting Action

Disabled Data read or written by the CPU is only directed to the

PCI VGA devices palette registers.

Enabled Data read or written by the CPU is directed to both the

PCI VGA devices palette registers and the ISA VGA

devices palette registers, permitting the palette

registers of both VGA devices to be identical.

Loading...

Loading...