Chapter 6 Digital I/O

© National Instruments 6-7 X Series User Manual

Routing DI Sample Clock to an Output Terminal

You can route DI Sample Clock out to any PFI <0..15> terminal. The PFI

circuitry inverts the polarity of DI Sample Clock before driving the PFI

terminal.

Other Timing Requirements

Your DAQ device only acquires data during an acquisition. The device

ignores DI Sample Clock when a measurement acquisition is not in

progress. During a measurement acquisition, you can cause your DAQ

device to ignore DI Sample Clock using the DI Pause Trigger signal.

The DI timing engine on your device internally generates DI Sample Clock

unless you select some external source. DI Start Trigger starts this timing

engine and either software or hardware can stop it once a finite acquisition

completes. When using the DI timing engine, you also can specify a

configurable delay from DI Start Trigger to the first DI Sample Clock

pulse.

By default, this delay is set to two ticks of the DI Sample Clock Timebase

signal.

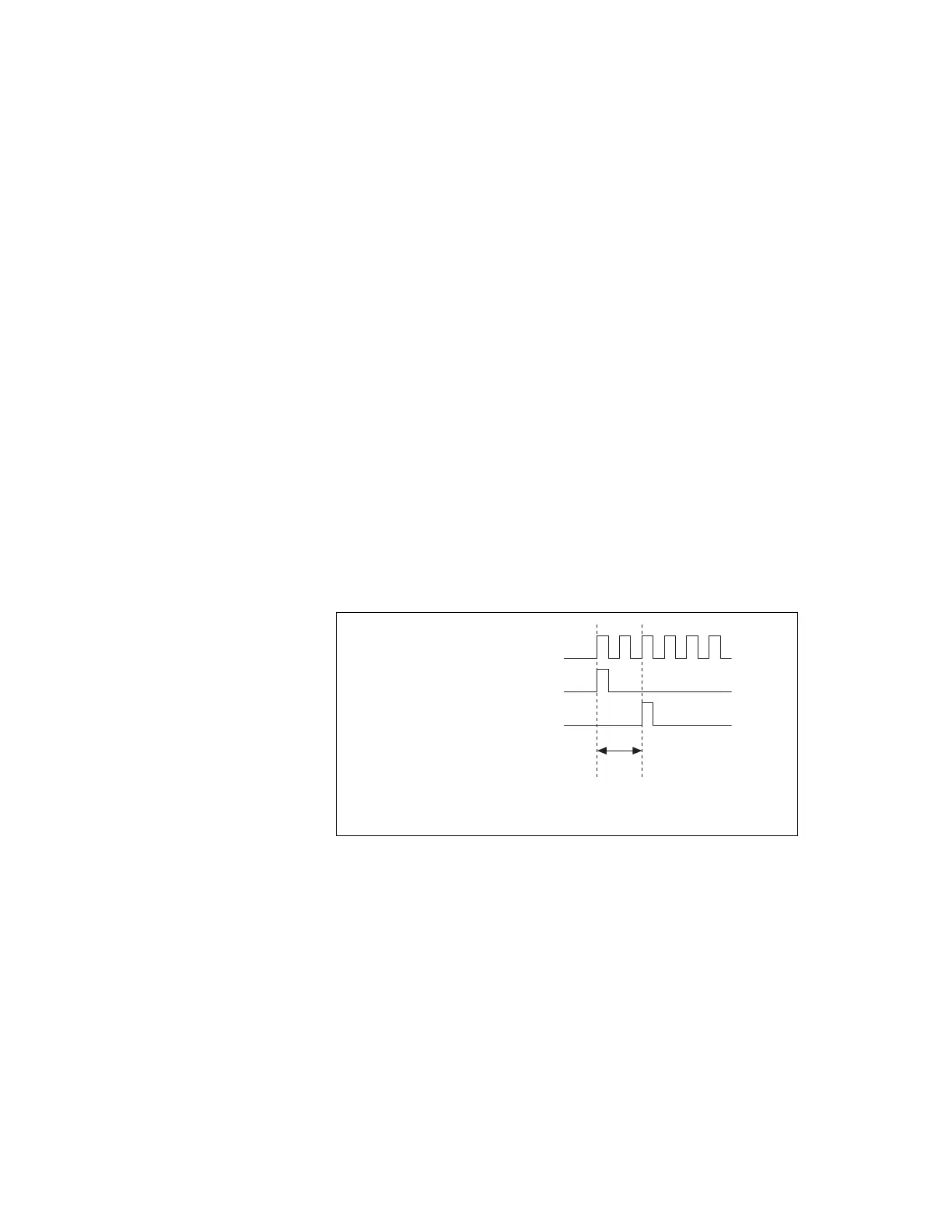

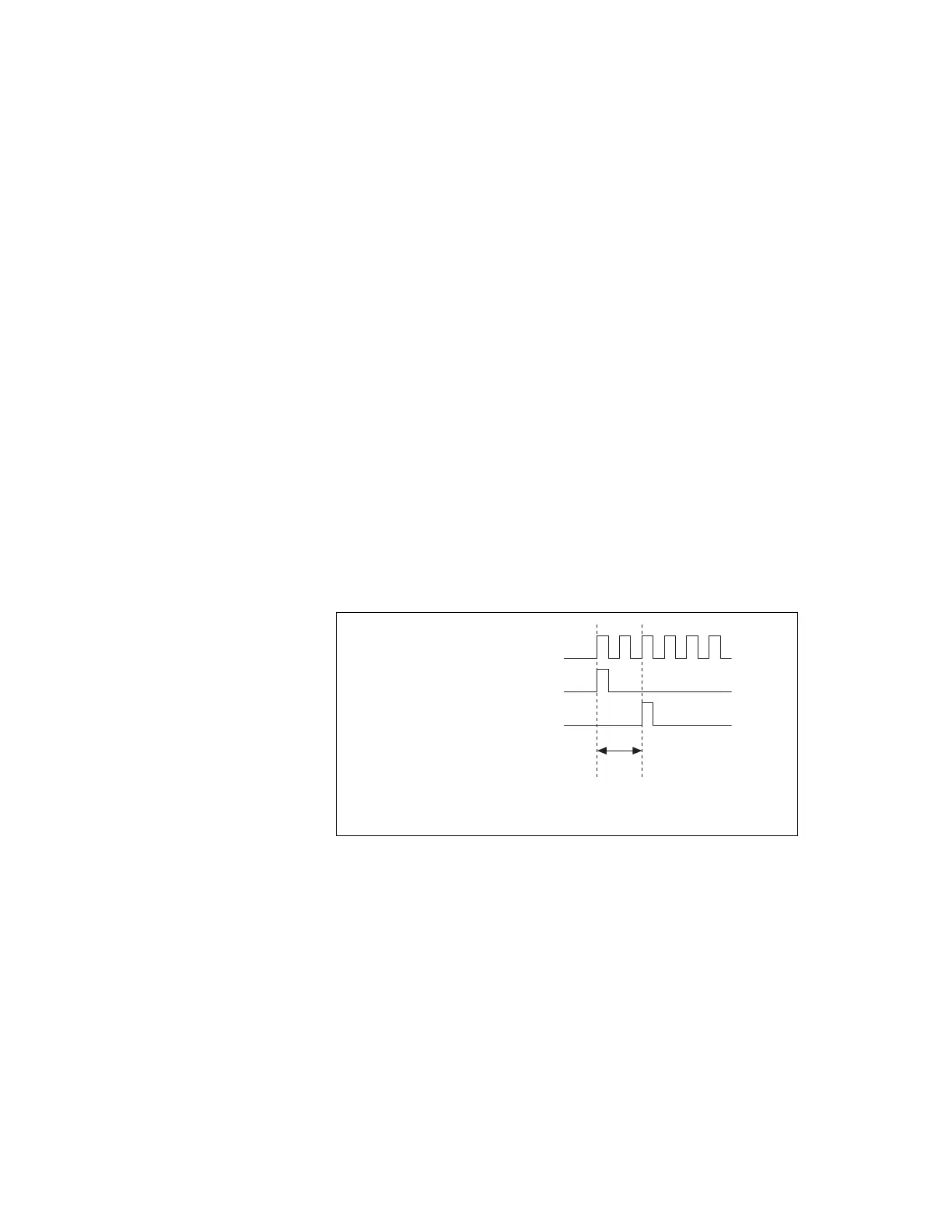

Figure 6-3. DI Sample Clock and DI Start Trigger

DI Sample Clock Timebase Signal

You can route any of the following signals to be the DI Sample Clock

Timebase (di/SampleClockTimebase) signal:

• 100 MHz Timebase (default)

• 20 MHz Timebase

• 100 kHz Timebase

DI Sample Clock Timebase

DI Start Trigger

DI Sample Clock

Delay

From

Start

Trigger

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...