MSM80C154S/83C154S/85C154HVS

44

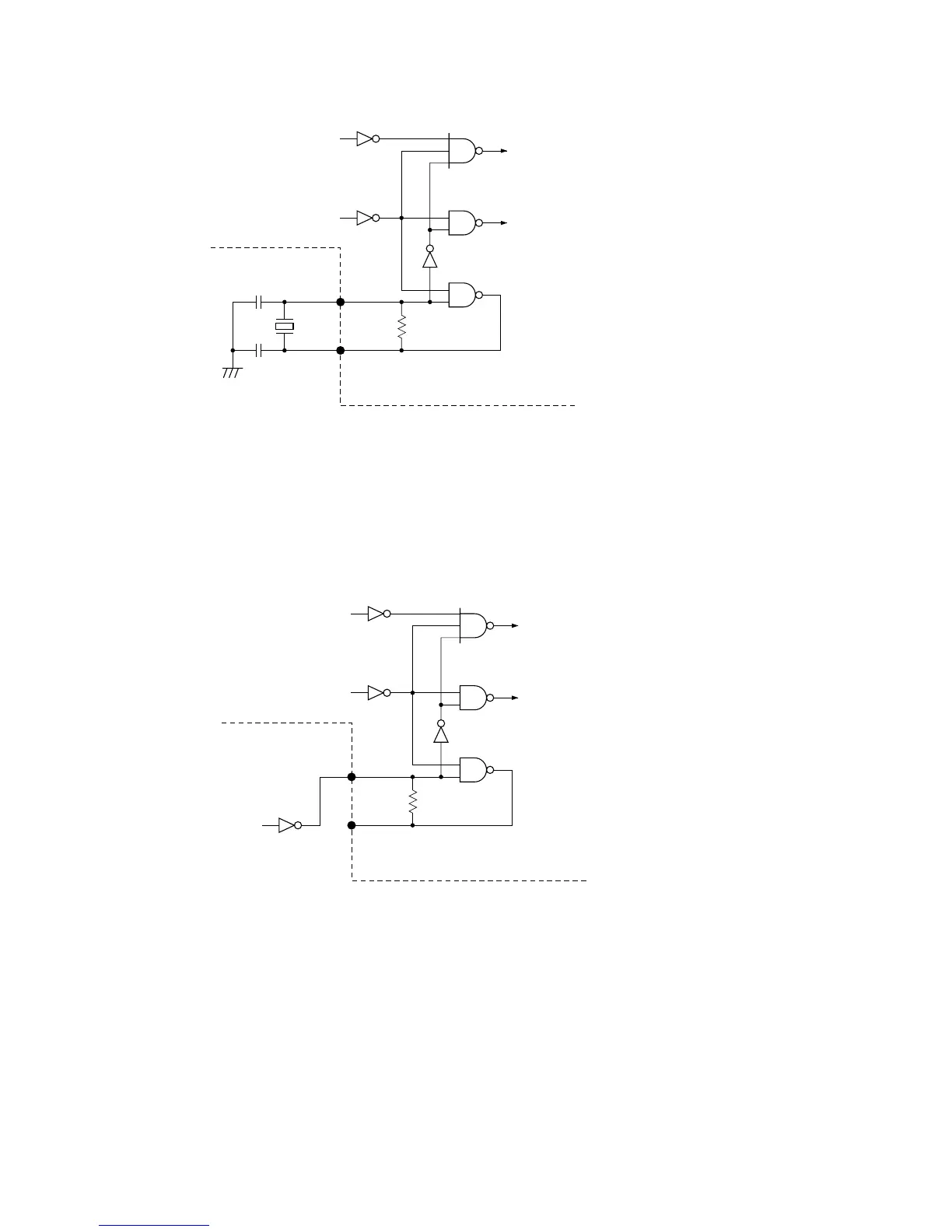

IDLE MODE

PD & HPD MODE

CPU CONTROL CLOCK

TIMER, S I/O & INTERRUPT

1MΩ

XTAL1

XTAL2

C

C

*

*

MSM80C154S/MSM83C154S

* The capacity of the compensating capacitor depends on the ceramic resonator.

* The XTAL1·2 frequency depends on VCC.

Figure 3-2 Ceramic resonator connection diagram

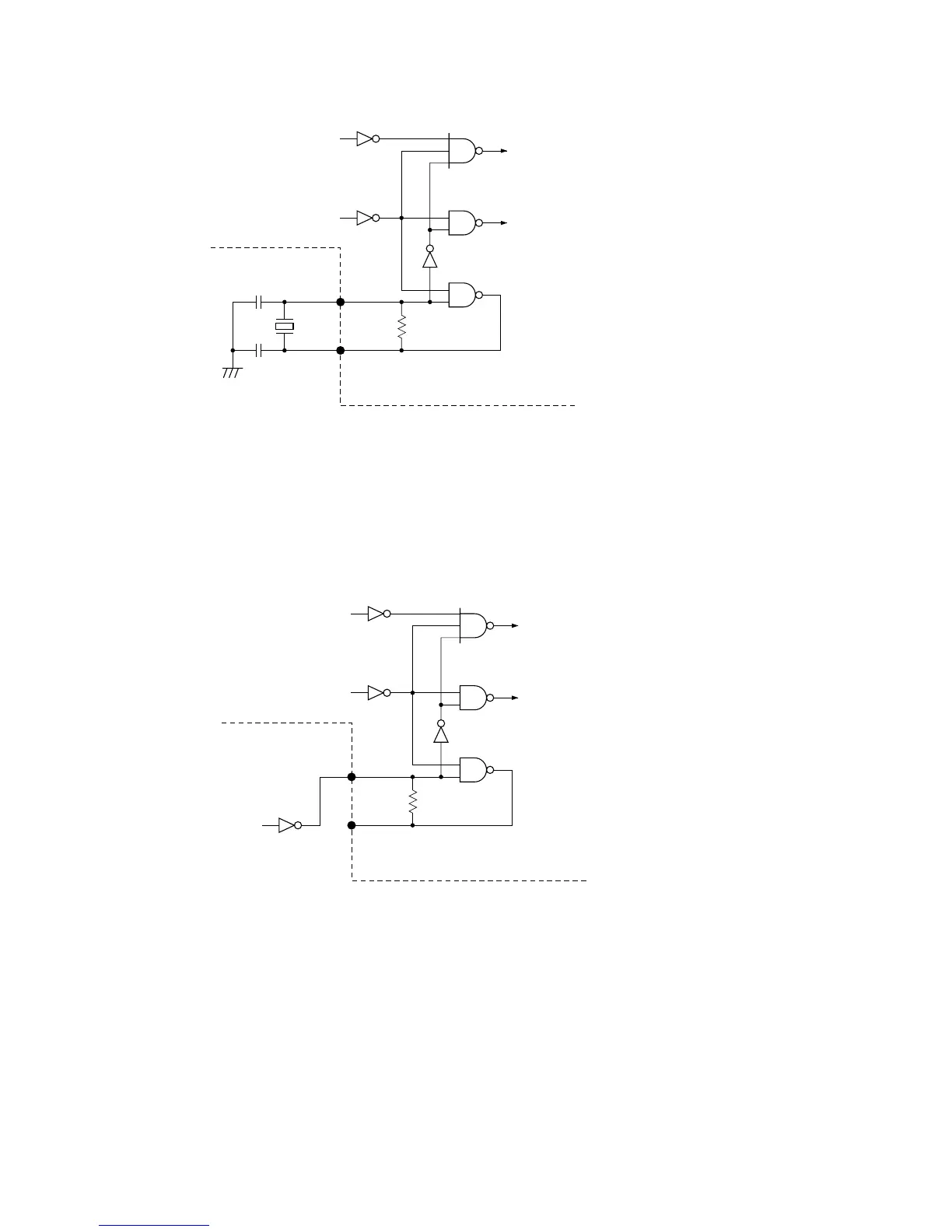

IDLE MODE

PD & HPD MODE

CPU CONTROL CLOCK

TIMER, S I/O & INTERRUPT

1MΩ

XTAL1

XTAL2

MSM80C154S/MSM83C154S

*CLOCK

74HC04

* Supply of 50% duty clock

Figure 3-3 External clock supply circuit

Loading...

Loading...