Smart Module Series

SG368Z_Series_Hardware_Design 75 / 113

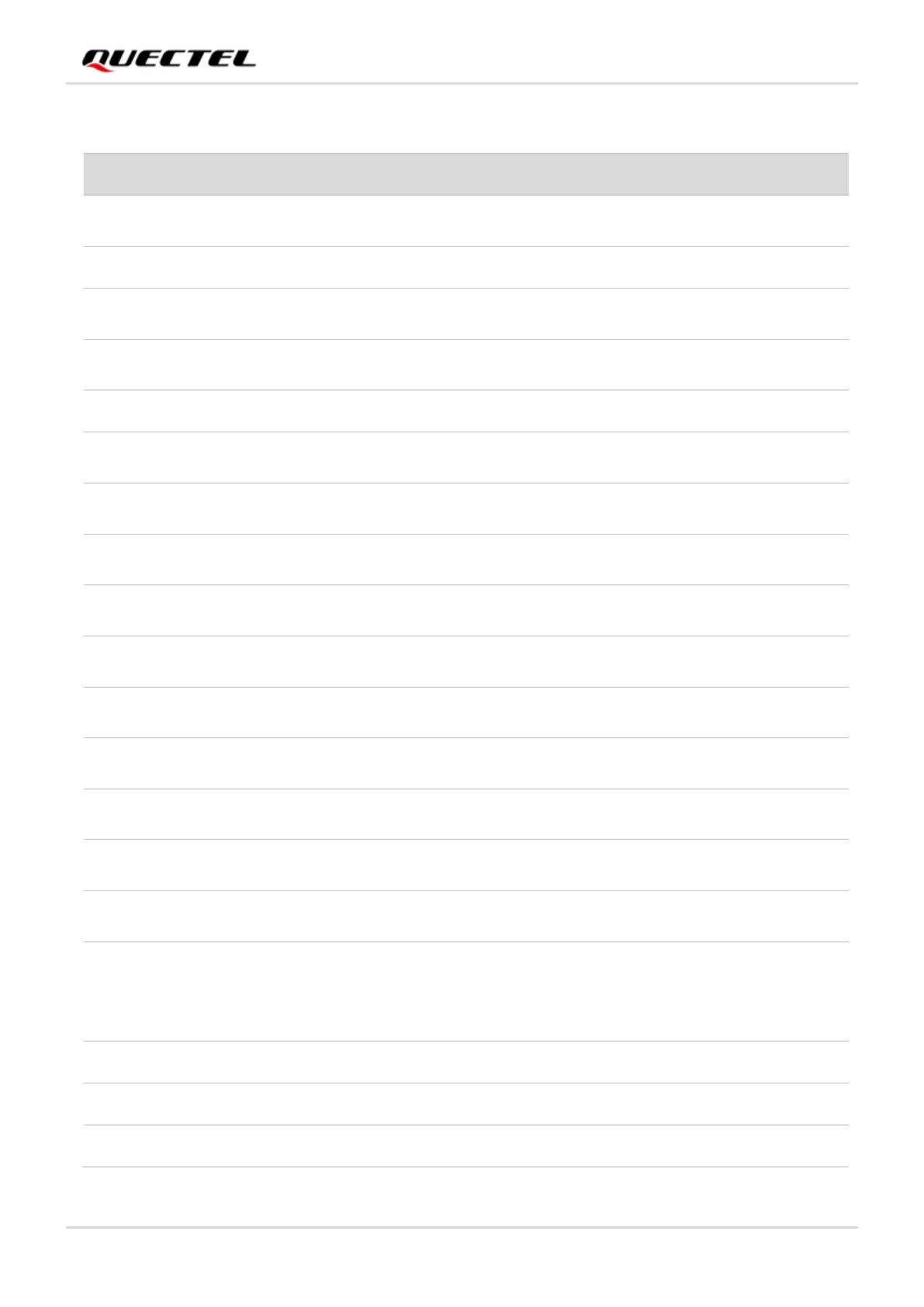

Table 32: Pins Description of RGMII Interfaces

RGMII0 receive data bit 0

Only SG368Z-AP supports

this pin.

RGMII0 receive data bit 1

RGMII0 receive data bit 2

Only SG368Z-AP supports

this pin.

RGMII0 receive data bit 3

Only SG368Z-AP supports

this pin.

Only SG368Z-AP supports

this pin.

RGMII0 transmit data bit 0

Only SG368Z-AP supports

this pin.

RGMII0 transmit data bit 1

Only SG368Z-AP supports

this pin.

RGMII0 transmit data bit 2

Only SG368Z-AP supports

this pin.

RGMII0 transmit data bit 3

Only SG368Z-AP supports

this pin.

Only SG368Z-AP supports

this pin.

Only SG368Z-AP supports

this pin.

RGMII0 management data

clock

Only SG368Z-AP supports

this pin.

RGMII0 management data

input/output

Only SG368Z-AP supports

this pin.

RGMII0 reference clock

output

The output frequency of

reference clock is 25 MHz.

The output frequency of

reference clock is 125 MHz;

Only SG368Z-AP supports

this pin.

RGMII1 receive data bit 0

RGMII1 receive data bit 1

RGMII1 receive data bit 2

Loading...

Loading...