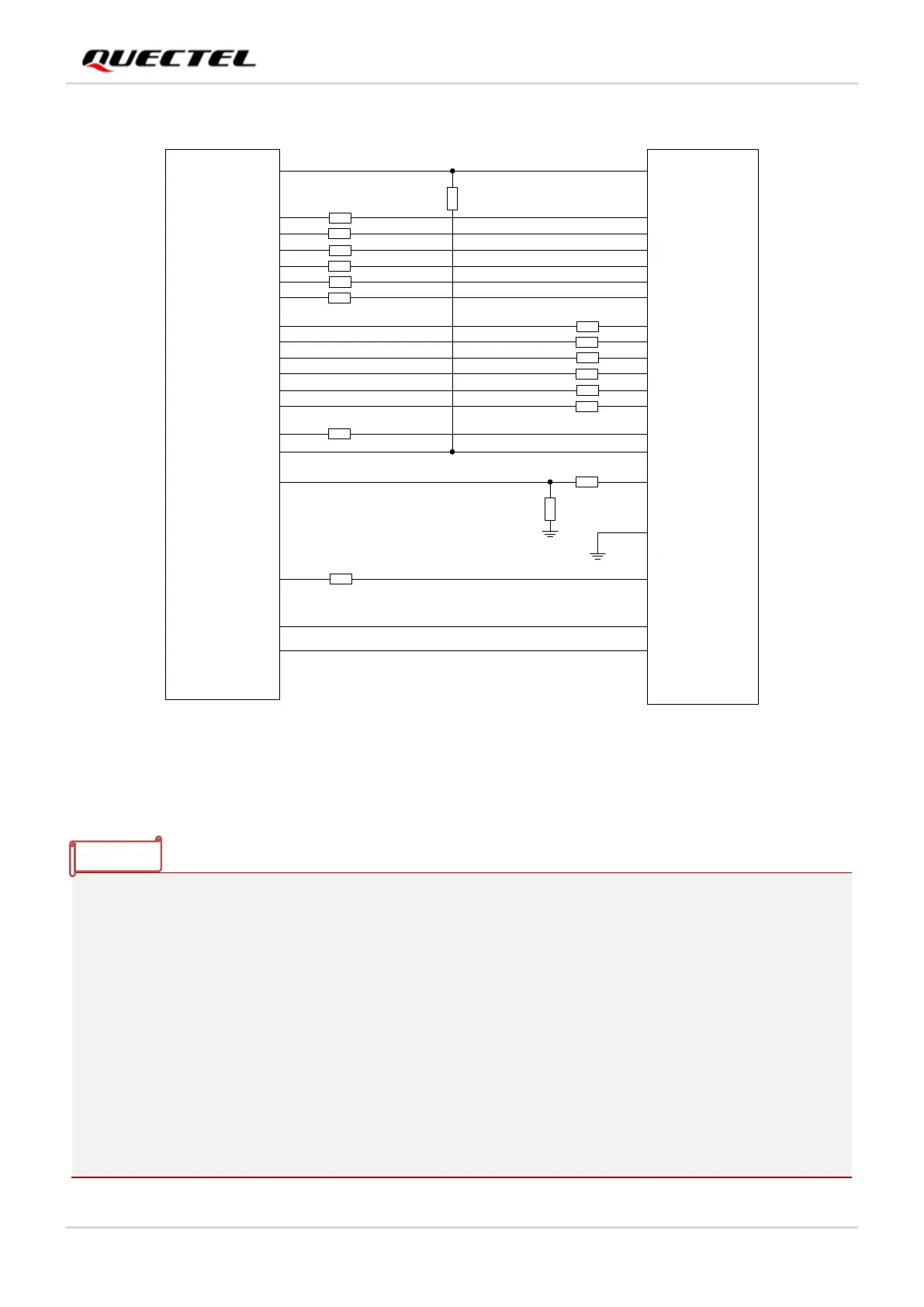

1. SG368Z-AP supports RGMII0 and RGMII1 interfaces, while SG368Z-WF only supports RGMII1

interface. RGMII0 uses GMAC0 controller and RGMII1 uses GMAC1 controller.

2. The power domain of RGMII interface is 1.8 V. Please pay attention to level matching with the voltage

of the PHY.

3. RGMII_MCLK is an optional function and can be left unconnected.

4. For the design of PHY end, please refer to the reference design of the PHY chip. The designs above

are for reference only.

5. If you choose the multiplexed SGMII interface, the used MDC/MDIO needs to match the GMACx

used, that is, if SGMII uses GMAC0, select RGMII0_MDC/RGMII0_MDIO, and if SGMII uses

GMAC1, select RGMII1_MDC/RGMII1_MDIO.

6. If you choose the multiplexed QSGMII interface, you can choose RGMII0_MDC/RGMII0_MDIO or

RGMII1_MDC/RGMII1_MDIO for MDC/MDIO functions.

Loading...

Loading...