User’s Manual 101

9.2 Parallel Port B

Parallel Port B, shown in Table 9-4, has six inputs and two outputs when used exclusively

as a parallel port.

When the slave port is enabled, parallel port lines PB2–PB7 are assigned to various slave

port functions. However, it is still possible to read PB0–PB5 using the Port B data register

even when lines PB2–PB7 are used for the slave port. It is also possible to read the signal

driving PB6 and PB7 (this signal is on the signaling lines from the slave port logic).

Regardless of whether the slave port is enabled, PB0 reflects the input of the pin unless

serial port B has its internal clock enabled, which causes this line to be driven by the serial

port clock. PB1 reflects the input of the pin unless serial port A has its internal clock

enabled.

On reset the output bits 6 and 7 are reset and the value output on pins PB6 and PB7 (pack-

age pins 99, 100) will also be low.

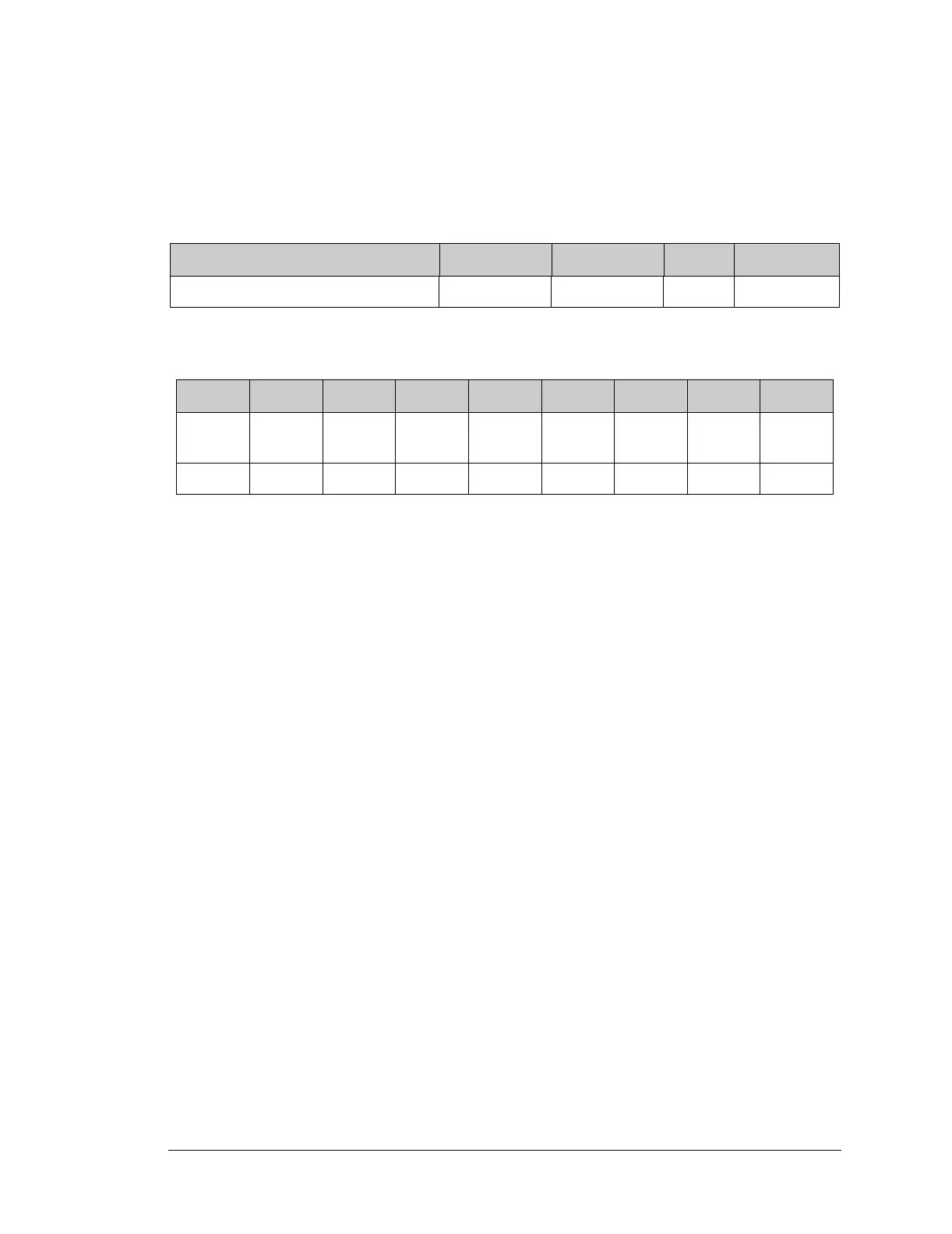

Table 9-3. Parallel Port B Registers

Register Name Mnemonic I/O address R/W Reset

Port B Data Register PBDR 0x40 R/W 00xxxxxx

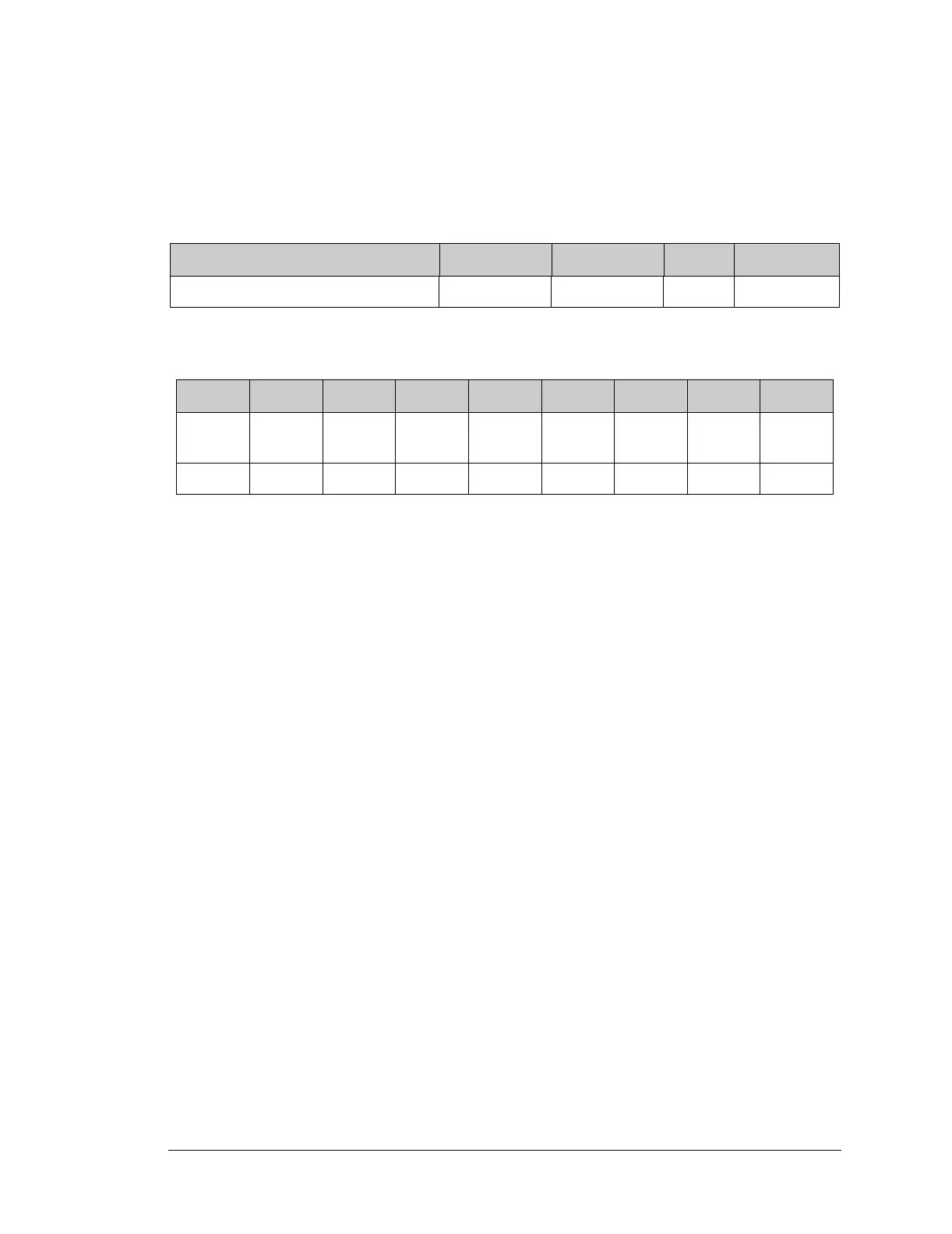

Table 9-4. Parallel Port B Data Register PBDR (adr = 0x040)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Read

Echo

drive

Echo

drive

PB5 in PB4 in PB3 in PB2 in PB1 in PB0 in

WritePB7PB6xxxxxx

Loading...

Loading...