User’s Manual 65

6. RABBIT INTERNAL I/O REGISTERS

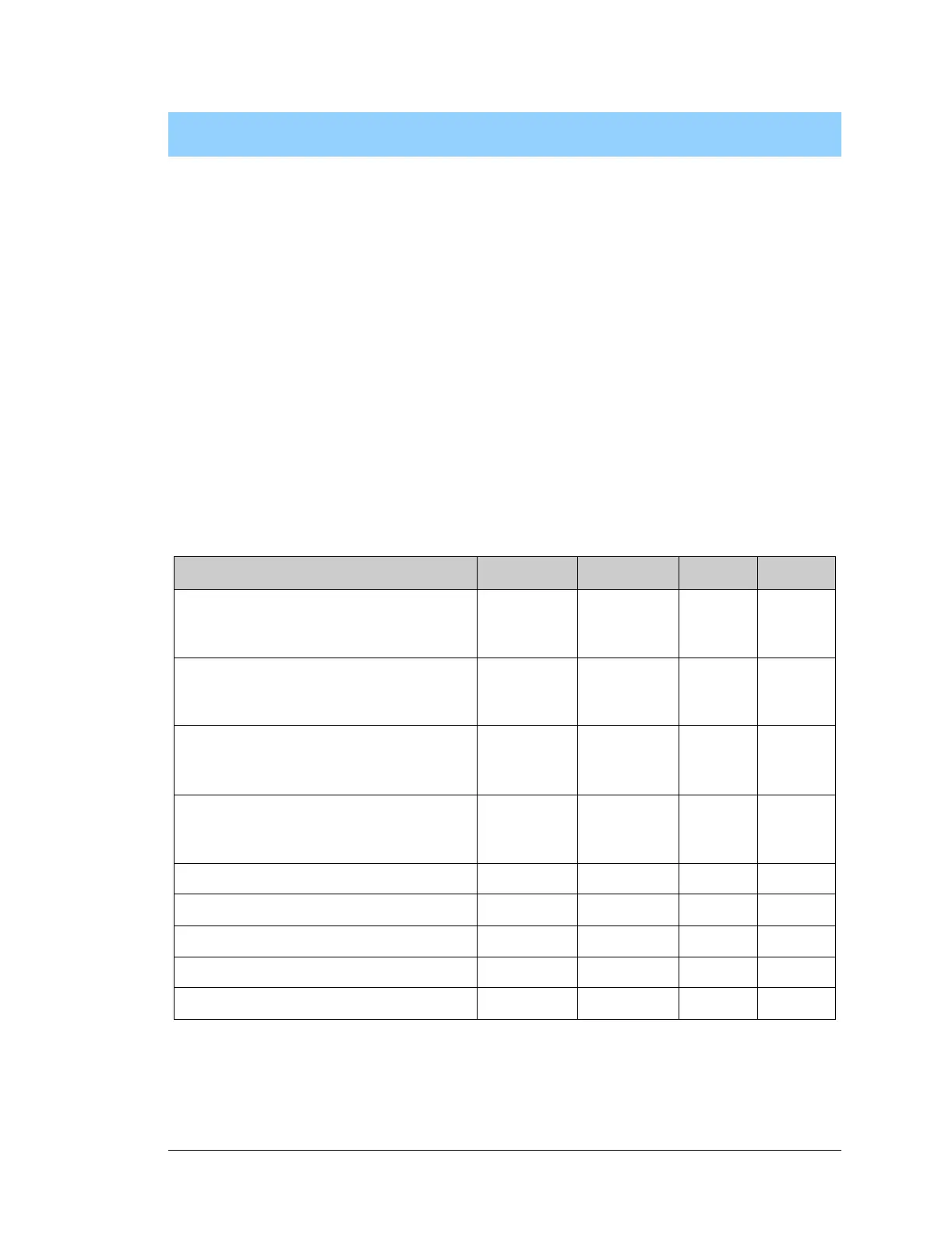

6.1 Default Values for all the Peripheral Control Registers

The default values for all of the peripheral control registers are shown in Table 6-1. Addi-

tional I/O registers were added in the Rabbit 2000 revisions as listed in the table. Refer to

Section B.2.1 for more information.

The registers within the CPU affected by a reset are the Stack Pointer (SP) register, the Pro-

gram Counter (PC) register, the IIR register, the EIR register, and the IP register. The IP

register is set to all ones (disabling all interrupts), while all of the other listed CPU registers

are reset to all zeros.

Table 6-1. Rabbit Internal I/O Registers

Register Name Mnemonic I/O Address R/W Reset

Data Segment Register (data segment memory

pointer—locates data segment in physical

memory)

DATASEG

(Z180 BBR)

0x12 R/W 00000000

Segment Size Register (specifies start of data

segment and start of stack segment in 64K

memory space)

SEGSIZE

(Z180 CBAR)

0x13 R/W 11111111

Stack Segment Register (stack segment mem-

ory pointer—locates stack segment in physical

memory)

STACKSEG

(Z180 CBR)

0x11 R/W 00000000

Global Control/Status Register (control of

clocks, periodic interrupts, and monitoring of

watchdog)

GCSR 0x0 R/W 11000000

Global Clock Double Register GCDR 0xF W xxxxx000

Global Clock Modulator 0 Register (Rev B–C) GCM0R 0x0A W 00000000

Global Clock Modulator 1 Register (Rev B–C) GCM1R 0x0B W 00000000

Global CPU Configuration Register (Rev A–C) GCPU 0x2E R 0xx00000

Global Output Control Register GOCR 0xE W 00000x00

Loading...

Loading...