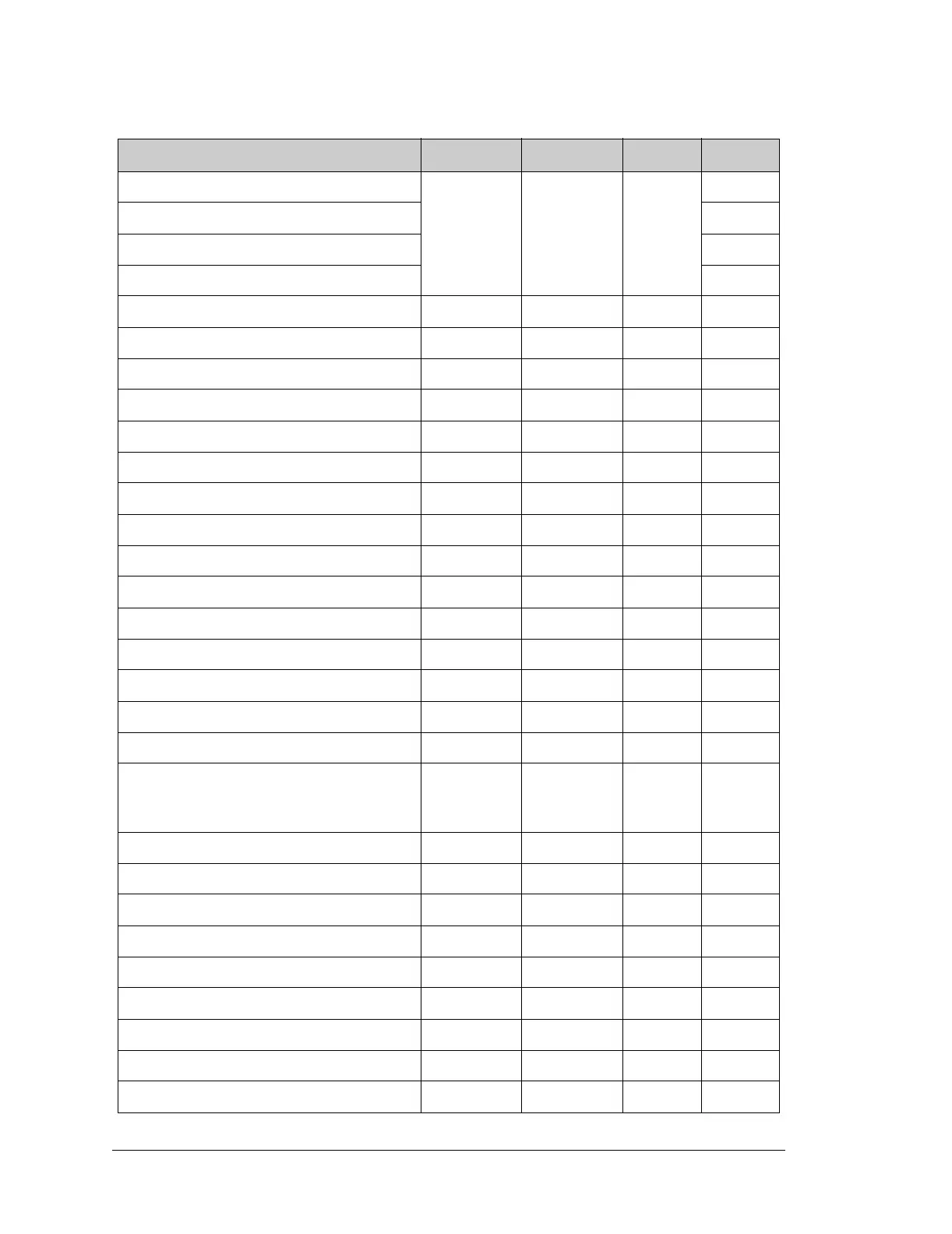

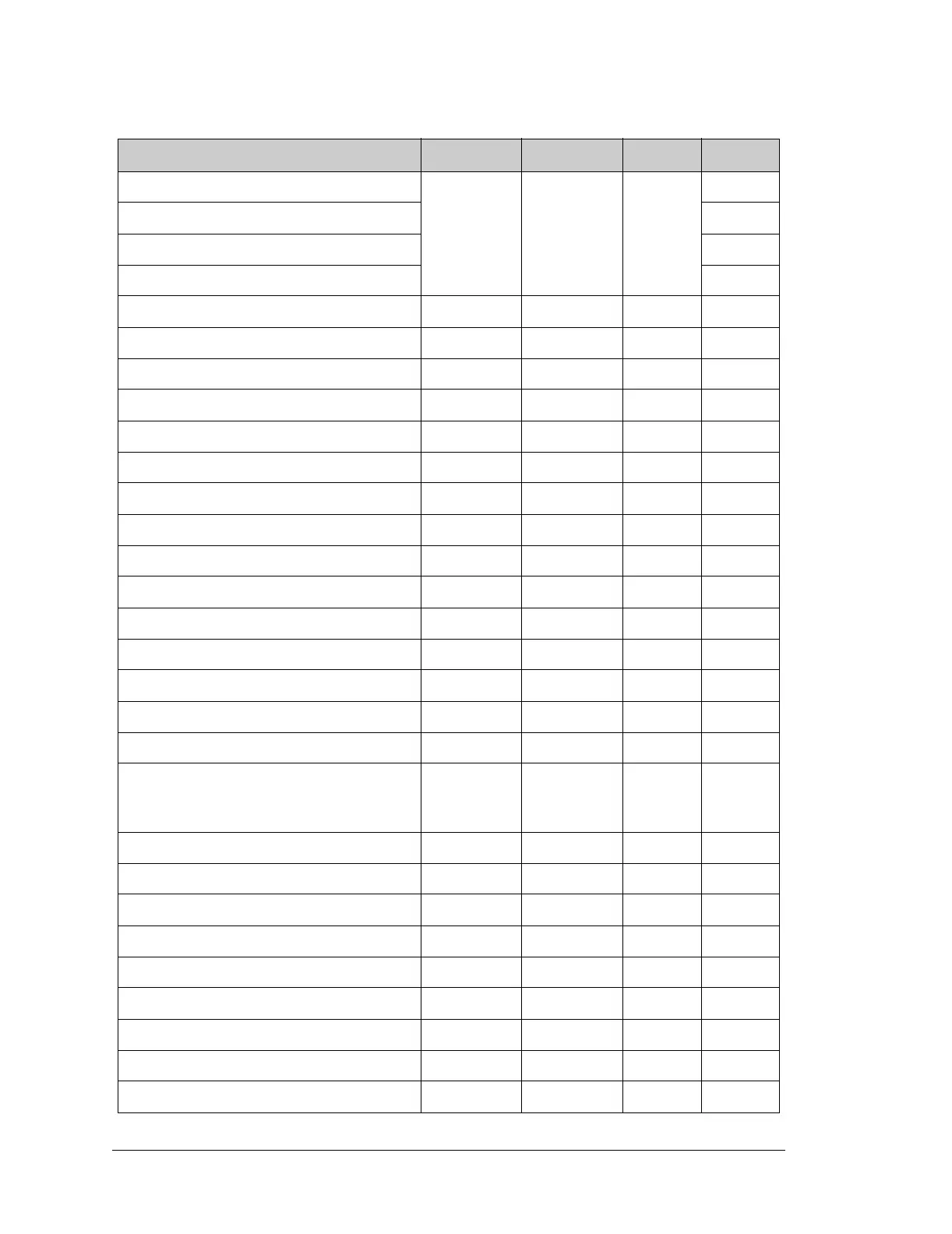

66 Rabbit 2000 Microprocessor

Rabbit 2000 Global Revision Register (Rev A–C)

GREV 0x2F R

0xx00000

Rabbit 2000A Global Revision Register (Rev A–C)

0xx00001

Rabbit 2000B Global Revision Register (Rev A–C)

0xx00010

Rabbit 2000C Global Revision Register (Rev A–C)

0xx00011

I/O Bank 0 Control Register IB0CR 0x80 W 00000xxx

I/O Bank 1 Control Register IB1CR 0x81 W 00000xxx

I/O Bank 2 Control Register IB2CR 0x82 W 00000xxx

I/O Bank 3 Control Register IB3CR 0x83 W 00000xxx

I/O Bank 4 Control Register IB4CR 0x84 W 00000xxx

I/O Bank 5 Control Register IB5CR 0x85 W 00000xxx

I/O Bank 6 Control Register IB6CR 0x86 W 00000xxx

I/O Bank 7 Control Register IB7CR 0x87 W 00000xxx

Interrupt 0 Control Register I0CR 0x98 W xx000000

Interrupt 1 Control Register I1CR 0x99 W xx000000

Memory Bank 0 Control Register (Rev A–C) MB0CR 0x14 W 00001000

Memory Bank 0 Control Register (original chip) MB0CR 0x14 W 00000000

Memory Bank 1 Control Register MB1CR 0x15 W xxxxxxxx

Memory Bank 2 Control Register MB2CR 0x16 W xxxxxxxx

Memory Bank 3 Control Register MB3CR 0x17 W xxxxxxxx

MMU Instruction/Data Register (controls I & D

space enable and battery switchover support

for /CS1)

MMIDR 0x10 R/W xxx00000

Memory Timing Control Register (Rev C) MTCR 0x19 W xxxx0000

Port A Data Register PADR 0x30 R/W xxxxxxxx

Port B Data Register PBDR 0x40 R/W 00xxxxxx

Port C Data Register PCDR 0x50 R/W x0x0x0x0

Port C Function Register PCFR 0x55 W x0x0x0x0

Port D Data Register PDDR 0x60 R/W xxxxxxxx

Port D Control Register PDCR 0x64 W xx00xx00

Port D Function Register PDFR 0x65 W xxxxxxxx

Port D Drive Control Register PDDCR 0x66 W xxxxxxxx

Table 6-1. Rabbit Internal I/O Registers (continued)

Register Name Mnemonic I/O Address R/W Reset

Loading...

Loading...