84 Rabbit 2000 Microprocessor

7.9 Rabbit Interrupt Structure

An interrupt causes a call to be executed, pushing the PC on the stack and starting to exe-

cute code at the interrupt vector address. The interrupt vector addresses have a fixed lower

byte value for all interrupts. The upper byte is adjustable by setting the registers EIR and

IIR for external and internal interrupts respectively. There are only two external interrupts

generated by transitions on certain pins in parallel port E.

The interrupt vectors are shown in Table 7-11.

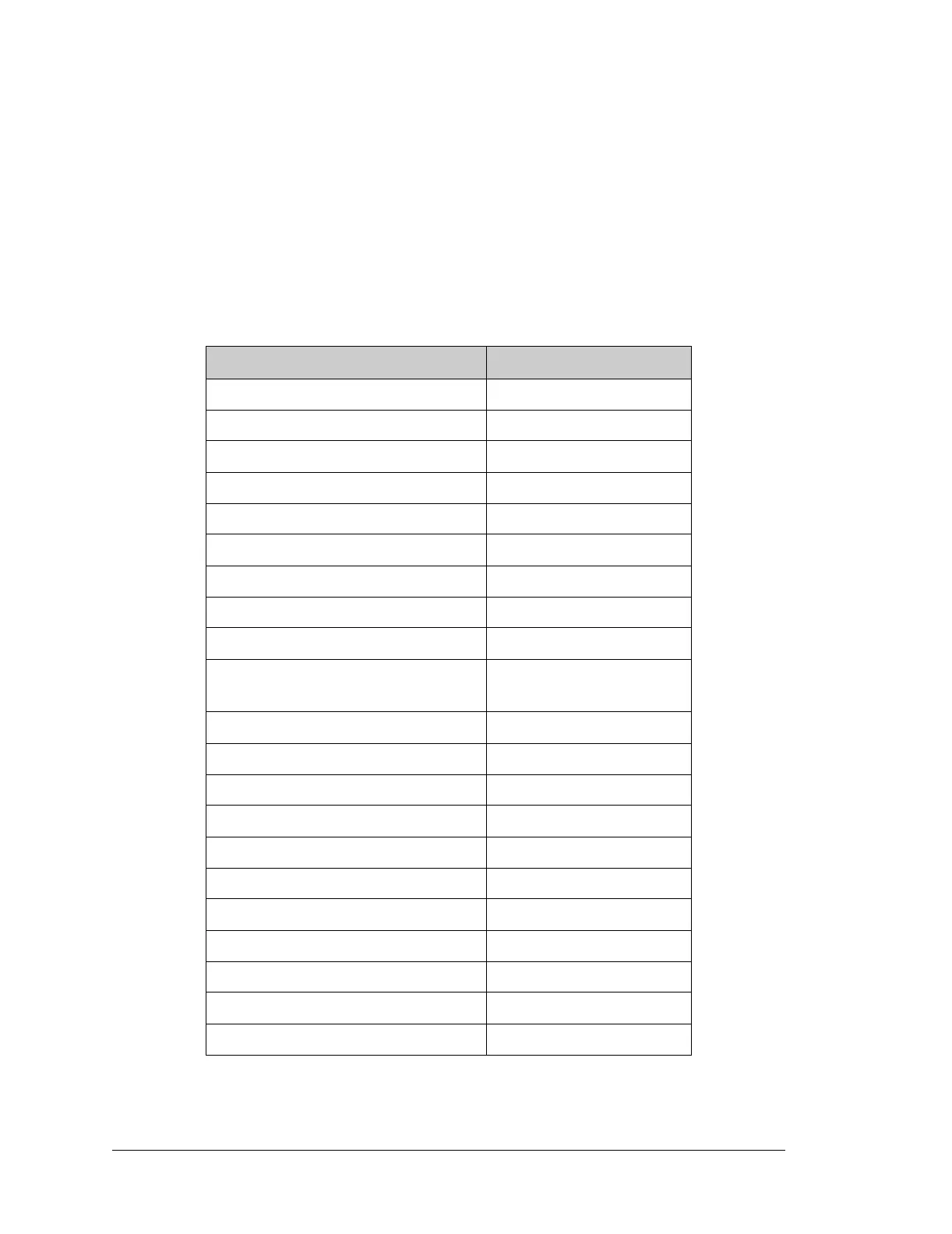

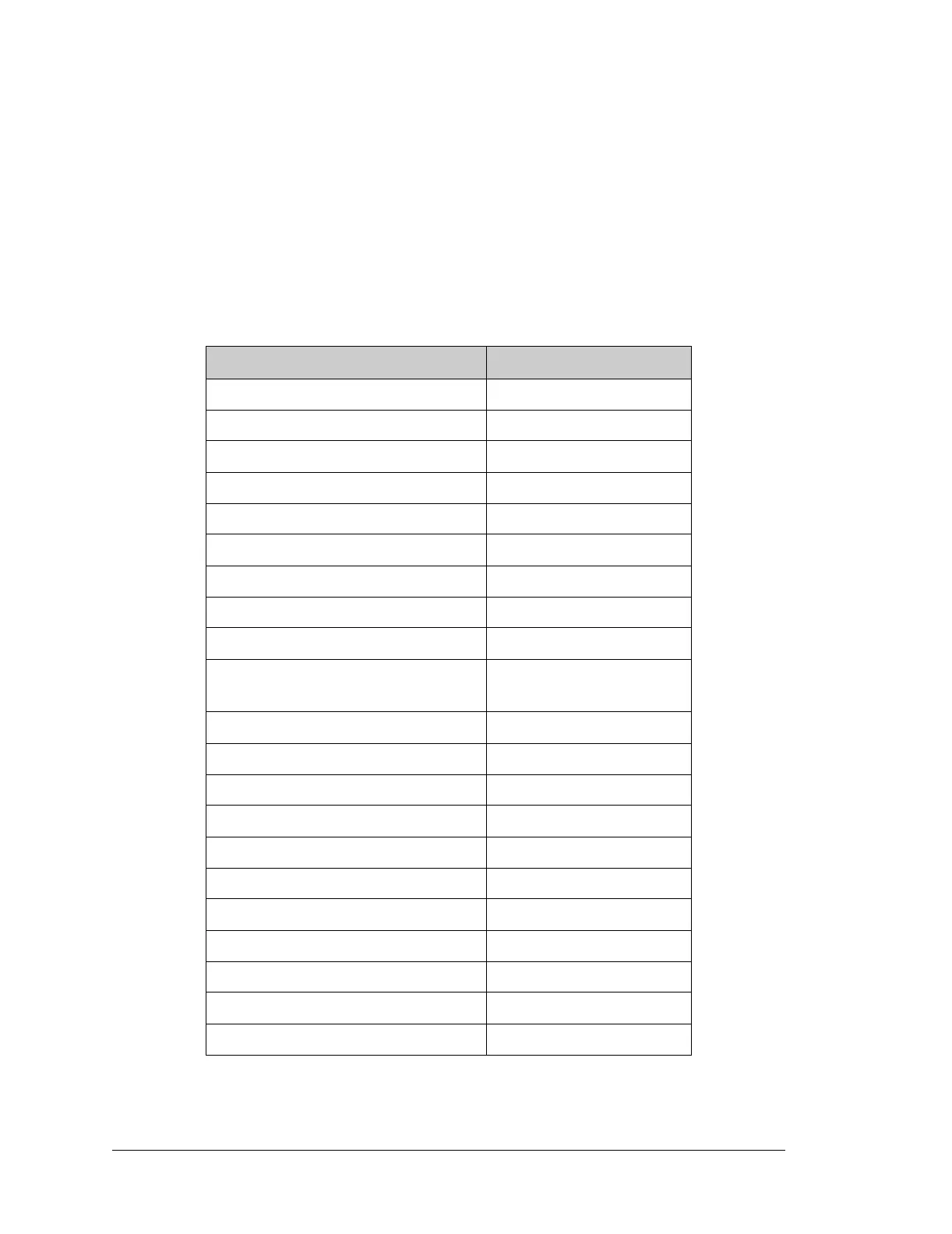

Table 7-11. Peripheral Device Address and Interrupt Vectors

On-Chip Peripheral ISR Starting Address

System Management (periodic interrupt) {IIR, 0x00}

Memory Management No interrupts

Slave Port {IIR, 0x80}

Parallel Port A No interrupts

Parallel Port B No interrupts

Parallel Port C No interrupts

Parallel Port D No interrupts

Parallel Port E No interrupts

External I/O Control No interrupts

External Interrupts

INT0 {EIR, 0x00}

INT1 {EIR, 0x10}

Timer A {IIR, 0xA0}

Timer B {IIR, 0xB0}

Serial Port A {IIR, 0xC0}

Serial Port B {IIR, 0xD0}

Serial Port C {IIR, 0xE0}

Serial Port D {IIR, 0xF0}

RST 10 instruction {IIR, 0x20}

RST 18 instruction {IIR, 0x30}

RST 20 instruction {IIR, 0x40}

RST 28 instruction {IIR, 0x50}

RST 38 instruction {IIR, 0x70}

Loading...

Loading...