104 Rabbit 2000 Microprocessor

• PDCR—Parallel port D control register. This register is used to control the clocking of

the upper and lower nibble of the final output register of the port. On reset, bits 0, 1, 4,

and 5 are reset to zero.

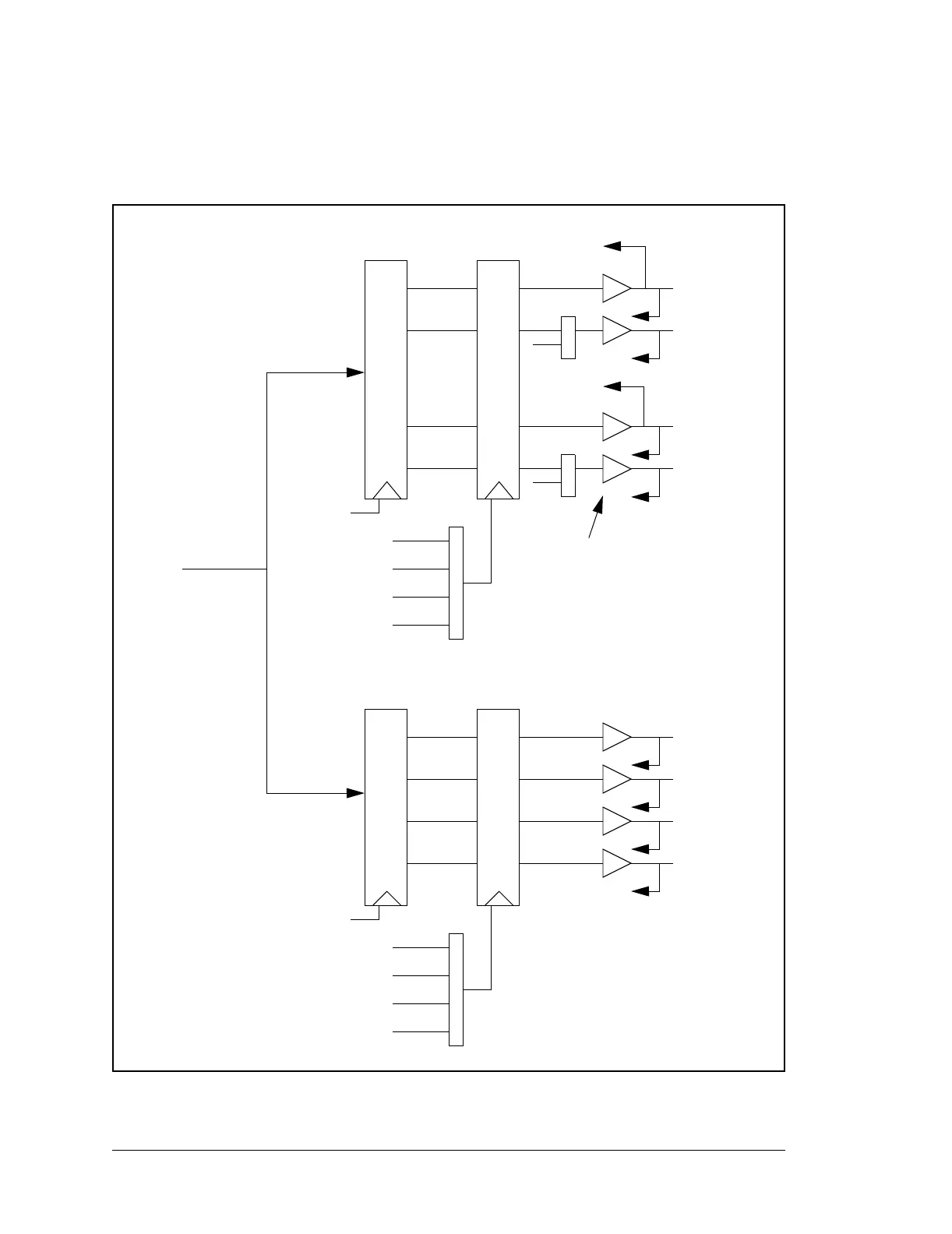

Figure 9-1. Parallel Port D Block Diagram

PD7

PD4

I/O Data

perclk/2

Timer A1

Timer B1

Timer B2

perclk/2

Timer A1

Timer B1

Timer B2

PD3

PD0

ATXA

ATXB

ARXA

ARXB

PD5

PD6

Inputs

Driver—optional open drain

Loading...

Loading...