User’s Manual 73

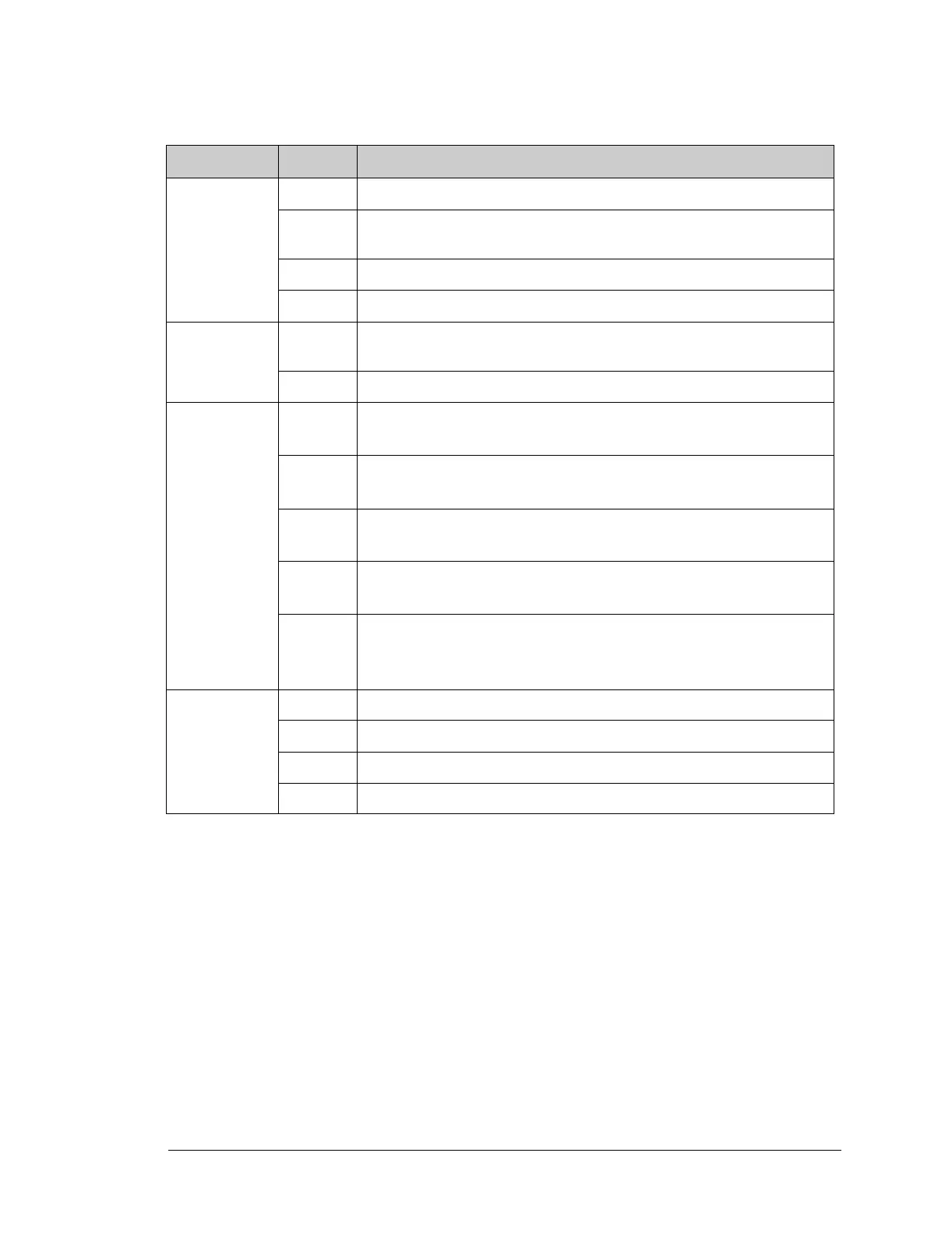

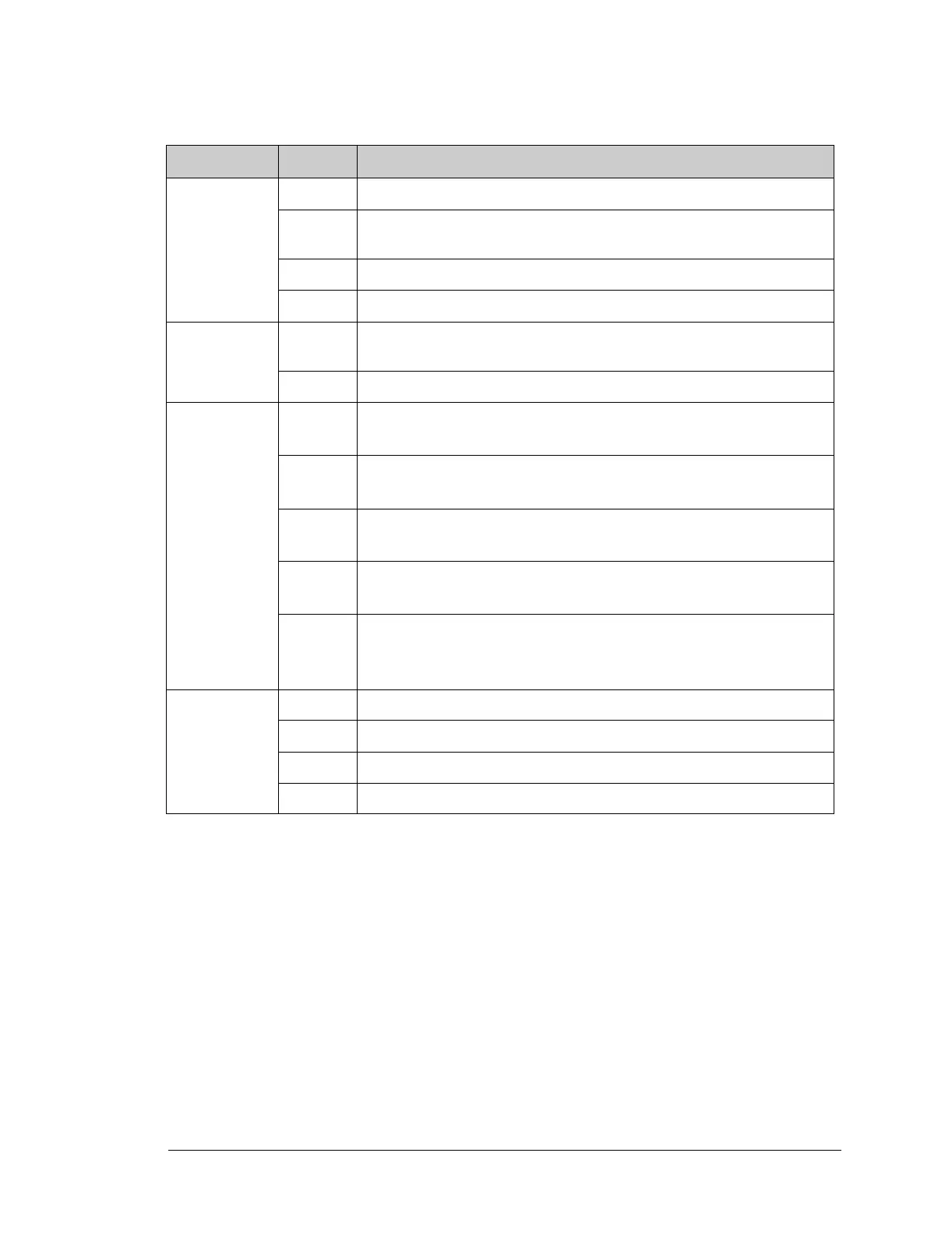

Table 7-1. Global Control/Status Register (I/O adr = 0x00)

Bit(s) Value Description

7:6 00 No reset or watchdog timer timeout since the last read.

(read only) 01

The watchdog timer timed out. These bits are cleared by a read of this

register.

10 This bit combination is not possible.

11 Reset occurred. These bits are cleared by a read of this register.

5 (write only) 0

Read this register to clear periodic interrupt request. This bit always read as

zero.

1 Force a periodic interrupt.

4:2 (write only) 000

Processor clock from the main oscillator, divided by eight.

Peripheral clock from the main oscillator, divided by eight.

001

Processor clock from the main oscillator, divided by eight.

Peripheral clock from the main oscillator, without divider.

01x

Processor clock from the main oscillator, without divider.

Peripheral clock from the main oscillator, without divider.

1x0

Processor clock from the 32 kHz oscillator, without divider.

Peripheral clock from the 32 kHz oscillator, without divider.

1x1

Processor clock from the 32 kHz oscillator, without divider.

Peripheral clock from the 32 kHz oscillator, without divider.

The main oscillator is turned off.

1:0 (write only) 00 Periodic interrupts are disabled.

01 Periodic interrupts use Interrupt Priority 1.

10 Periodic interrupts use Interrupt Priority 2.

11 Periodic interrupts use Interrupt Priority 3.

Loading...

Loading...