274 Rockwell Automation Publication 1766-UM001O-EN-P - September 2021

Appendix F MicroLogix 1400 Distributed Network Protocol

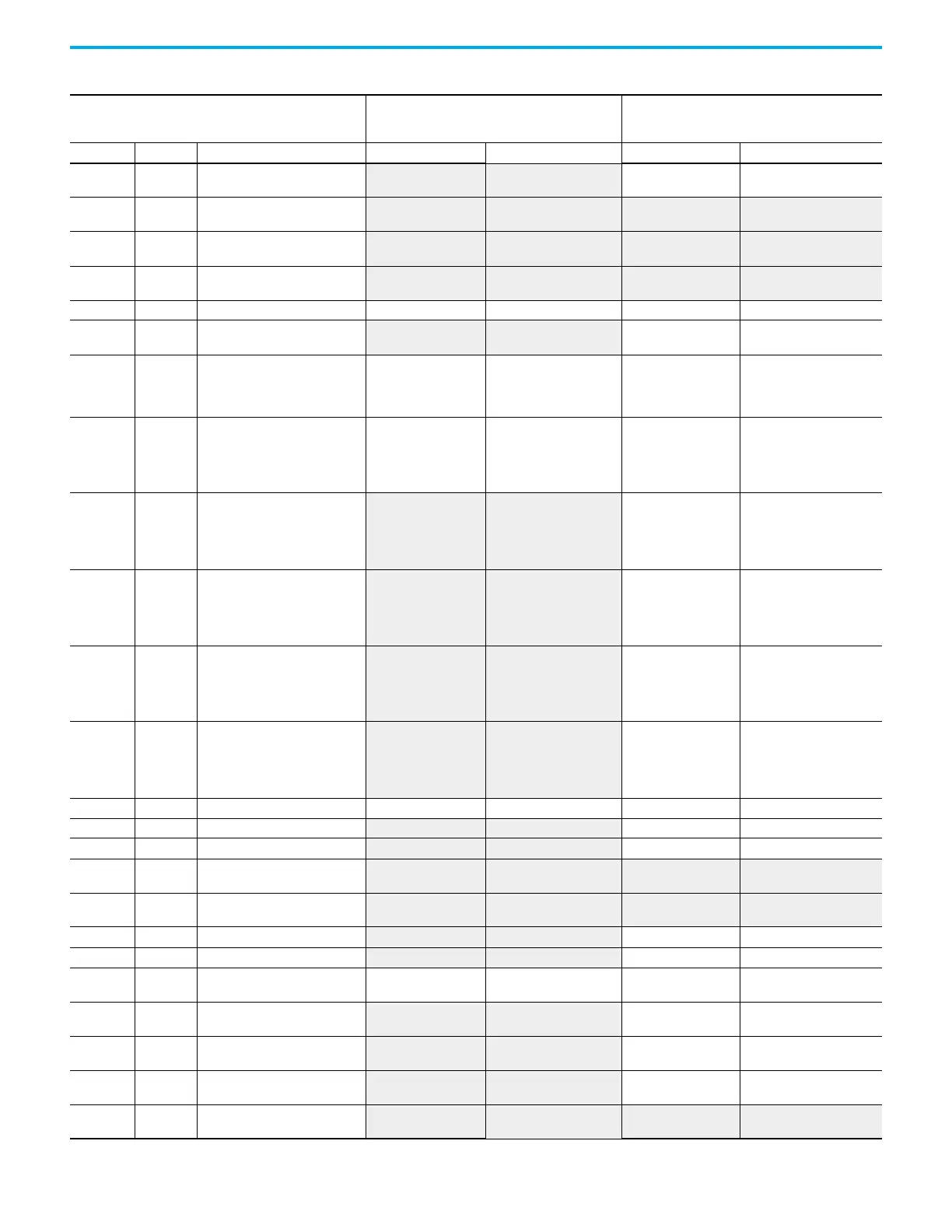

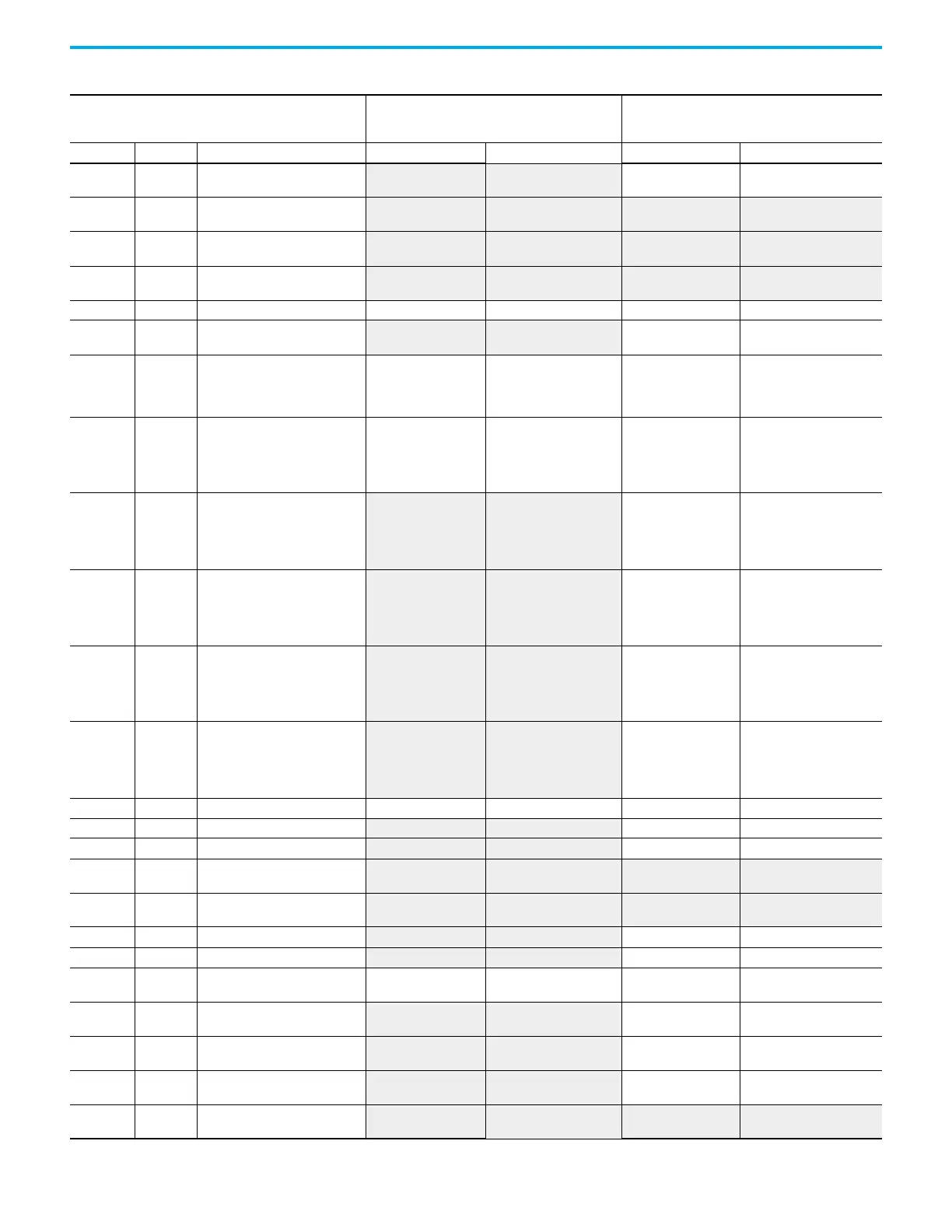

40

Double-bit Binary Input Event – Any

Variation

1 (read)

06 (no range, or all)

07, 08 (limited qty)

41

Double-bit Binary Input Event –

Without time

1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

42

Double-bit Binary Input Event – With

absolute time

1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

43

Double-bit Binary Input Event – With

relative time

1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

10 0 Binary Output – Any Variation 1 (read) 06 (no range, or all)

10 2

Binary Output – Output status with

flags

1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

12 1

Binary Command – Control relay

output block (CROB)

3 (select)

4 (operate)

5 (direct op)

6 (dir. op, no ack)

17, 28 (index) 129 (response) echo of request

20 0 Counter – Any Variation

1 (read)

7 (freeze)

8 (freeze noack)

9 (freeze clear)

10 (frz. cl. noack)

06 (no range, or all)

20 1 Counter – 32-bit with flag

1 (read)

7 (freeze)

8 (freeze noack)

9 (freeze clear)

10 (frz. cl. noack)

06 (no range, or all) 129 (response) 00, 01 (start-stop)

20 2 Counter – 16-bit with flag

1 (read)

7 (freeze)

8 (freeze noack)

9 (freeze clear)

10 (frz. cl. noack)

06 (no range, or all) 129 (response) 00, 01 (start-stop)

20 5 Counter – 32-bit without flag

1 (read)

7 (freeze)

8 (freeze noack)

9 (freeze clear)

10 (frz. cl. noack)

06 (no range, or all) 129 (response) 00, 01 (start-stop)

20 6 Counter – 16-bit without flag

1 (read)

7 (freeze)

8 (freeze noack)

9 (freeze clear)

10 (frz. cl. noack)

06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 0 Frozen Counter – Any Variation 1 (read) 06 (no range, or all)

21 1 Frozen Counter – 32-bit with flag

1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 2 Frozen Counter – 16-bit with flag 1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 5

Frozen Counter – 32-bit with flag

and time

1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 6

Frozen Counter – 16-bit with flag

and time

1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 9 Frozen Counter – 32-bit without flag 1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

21 10 Frozen Counter – 16-bit without flag

1 (read) 06 (no range, or all) 129 (response) 00, 01 (start-stop)

22 0 Counter Event – Any Variation 1 (read)

06 (no range, or all)

07, 08 (limited qty)

22 1 Counter Event – 32-bit with flag

1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

22 2 Counter Event – 16-bit with flag 1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

23 0

Frozen Counter Event – Any

Variation

1 (read)

06 (no range, or all)

07, 08 (limited qty)

23 1

Frozen Counter Event – 32-bit with

flag

1 (read)

06 (no range, or all)

07, 08 (limited qty)

129 (response)

130 (unsol. resp)

17, 28 (index)

Table 37 - Implementation Table for Series A controllers (Continued)

DNP Object Group & Variation

Request

DNP3 Master may issue

Controller must parse

Response

DNP3 Master must parse

Controller may issue

Group Num Var Num Description Function Codes (dec) Qualifier Codes (hex) Function Codes (dec) Qualifier Codes (hex)

Loading...

Loading...