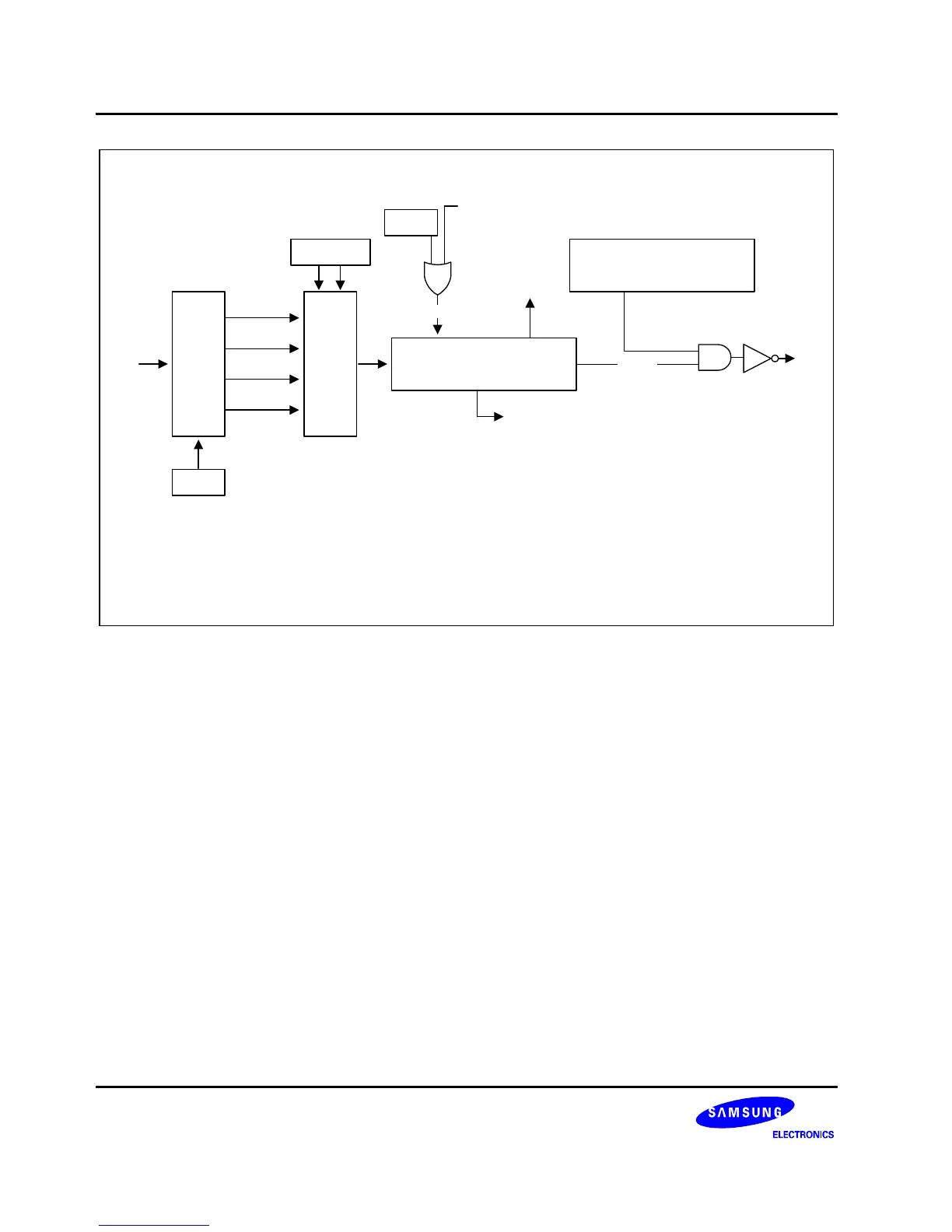

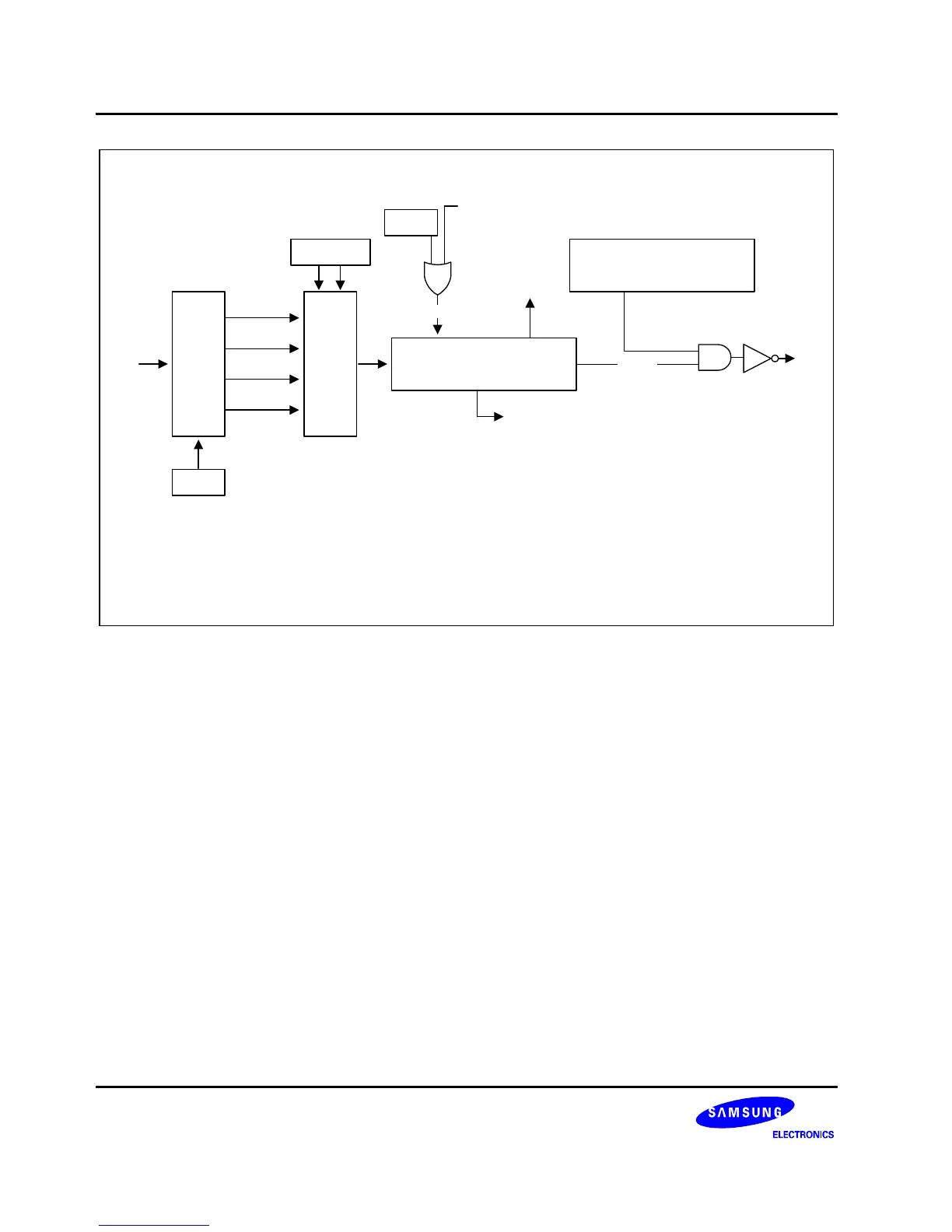

BASIC TIMER S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X

10-4

NOTE:

During a power-on reset operation, the CPU is idle during the required oscillation

stabilization interval (until bit 4 of the basic timer counter overflows).

MUX

f

XX

/4096

DIV

f

XX

/1024

f

XX

/128

f

XX

/16

f

XX

Bits 3, 2

Bit 0

Basic Timer Control Register

(Write '1010xxxxB' to Disable)

Clear

Bit 1

RESET or STOP

Data Bus

8-Bit Up Counter

(BTCNT, Read-Only)

Start the CPU

(note)

OVF

RESET

u

Figure 10-2. Basic Timer Block Diagram

Loading...

Loading...