LC-26SA1E/RU, LC-32SA1E/RU

7 – 9

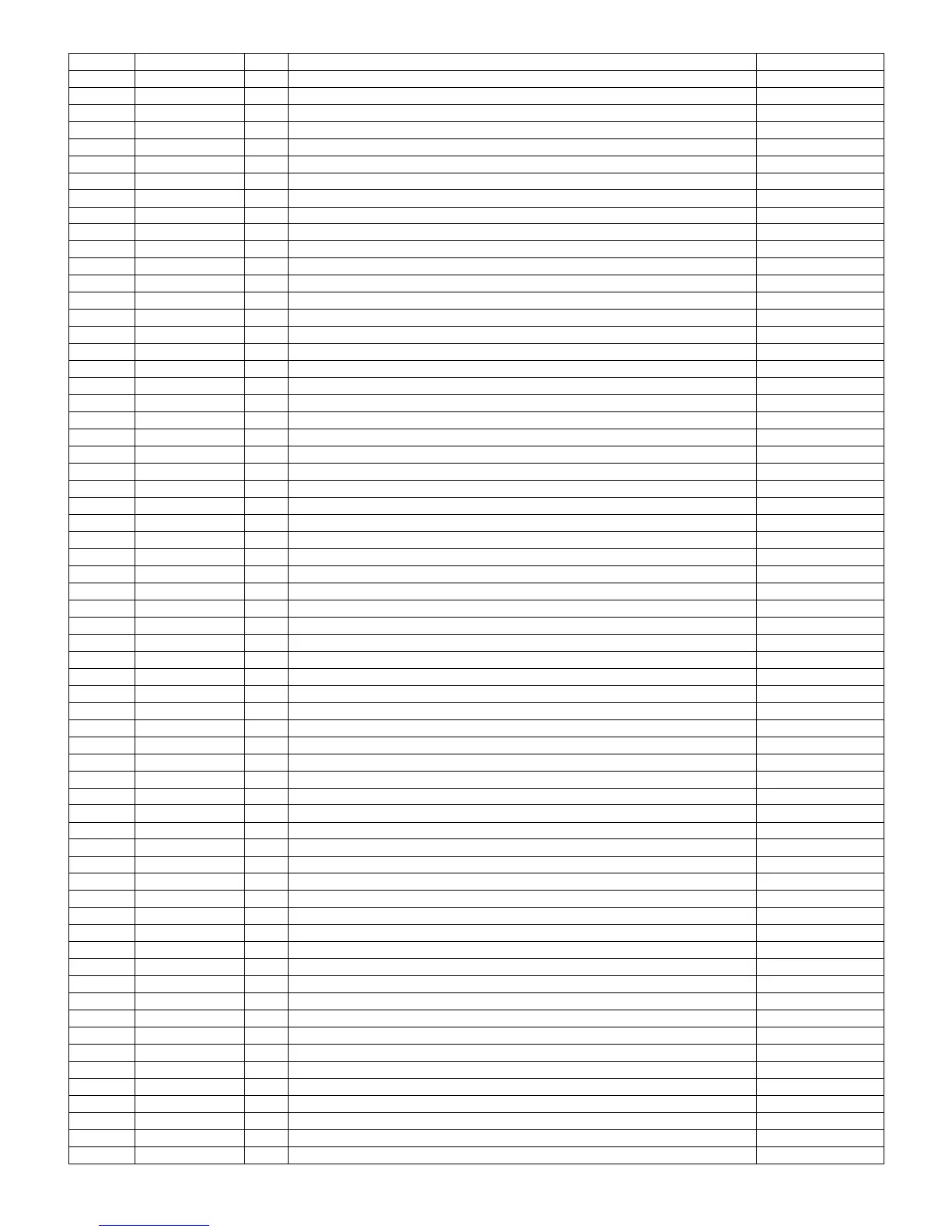

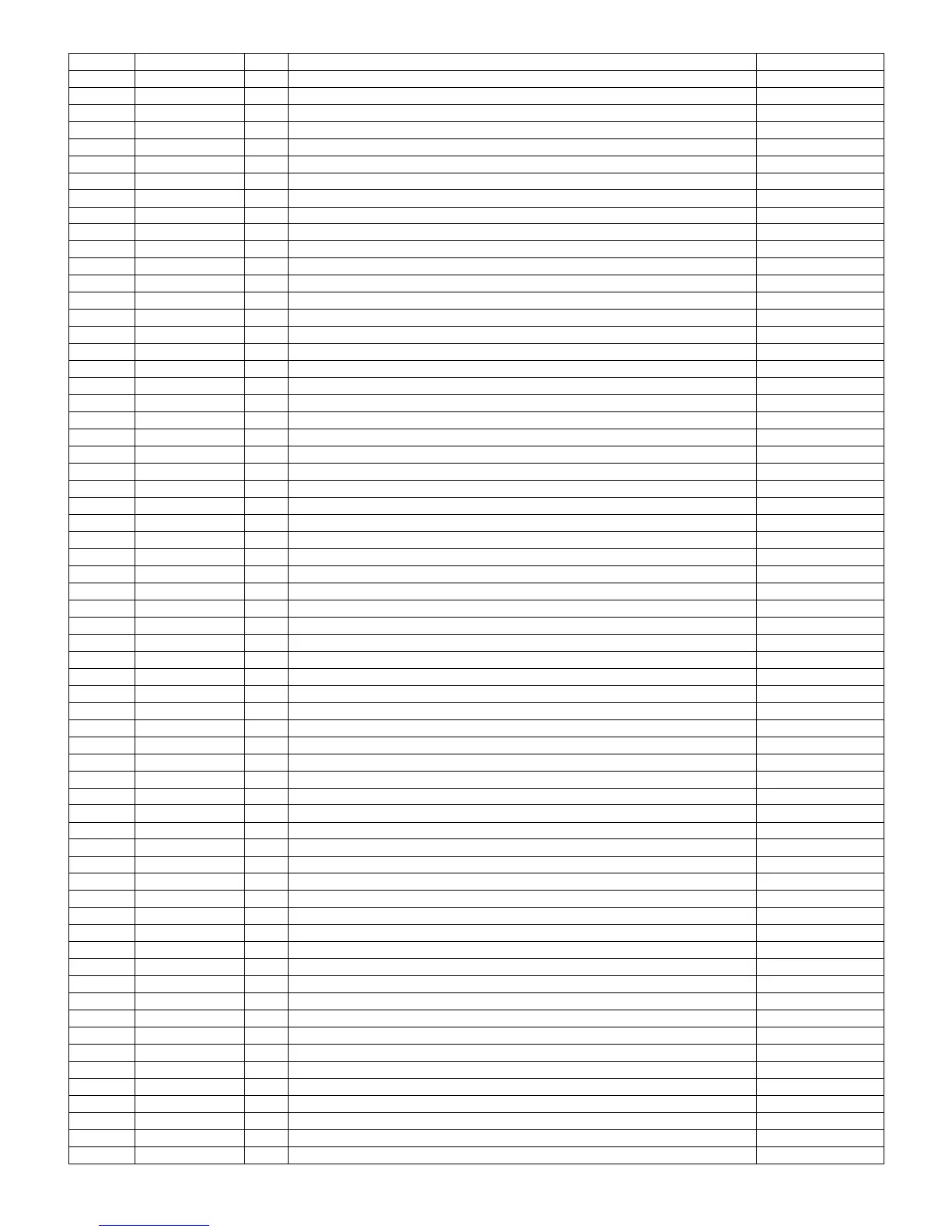

95 GND3.3IO1 – Ground Digital Input/Output Port 1 GND

96 VSUP3.3IO1 – Supply Voltage Input/Output Port 1, 3.3 V 3.3V

97 OSDCLK I/O Graphic Clock Input/Output open

98 OSDFSW I/O Graphic Fast Switch Input/Output open

99 P3_7 I/O Port3,bit7 Input/Output HP JSW (HP PLUG)

100 P3_6 I/O Port3,bit6 Input/Output HOTP_CONT1

101 P3_5 I/O Port3,bit5 Input/Output HOTP_CONT0

102 P3_4 I/O Port3,bit4 Input/Output HDMI_INT

103 OSDB1 I/O Graphic Blue 1 Input/Output open

104 OSDB0 I/O Graphic Blue 0 Input/Output open

105 P3_3 I/O Port3,bit3 Input/Output P3_3

106 P3_2 I/O Port3,bit2 Input/Output open

107 OSDG1 I/O Graphic Green 1 Input/Output open

108 OSDG0 I/O Graphic Green 0 Input/Output open

109 P3_1 I/O Port3,bit1 Input/Output BL_ERR

110 P3_0 I/O Port3,bit0 Input/Output DTM_IRQ

111 OSDR1 I/O Graphic Red 1 Input/Output open

112 OSDR0 I/O Graphic Red 0 Input/Output (LSB) Open

113 GND3.3IO1 – Ground Digital Input/Output Port 1 GND

114 VSUP3.3IO1 – Supply Voltage Input/Output Port 1, 3.3 V 3.3V

115 P2_7 I/O Port2,bit7 Input/Output FPGA_SDA

116 P2_6 I/O Port2,bit6 Input/Output FPGA_SCK

117 P4_1 I/O Port4,bit1 Input/Output FPGA_SDE

118 P4_0 I/O Port4,bit0 Input/Output SVIJSW

119 P4_3 I/O Port4,bit3 Input/Output HSYNC_OSC

120 P4_2 I/O Port4,bit2 Input/Output VSYNC_OSC

121 PCLK2 O Flat Panel Control Clock 2 Output Open

122 PCLK1 O Flat Panel Control Clock 1 Output PCLK

123 GND1.8DIG – Ground Digital Core GND

124 VSUP1.8DIG – Supply Voltage Digital Core, 1.8 V 1.8V

125 LVDSA_4P O LVDS Channel 1 bit 4 Positive Output 2) Open

126 LVDSA_4N O LVDS Channel 1 bit 4 Negative Output 2) Open

127 VSUP3.3LVDS – Supply Digital Voltage LVDS2) Port, 3.3 V 3.3V

128 LVDSA_3P O LVDS Channel 1 bit 3 Positive Output 2) LVDS3P

129 LVDSA_3N O LVDS Channel 1 bit 3 Negative Output 2) LVDS3N

130 GND3.3LVDS – Ground Digital LVDS2), 3.3 V GND

131 LVDSA_CLKP O LVDS Channel 1 Clock Positive Output 2) LVDSCP

132 LVDSA_CLKN O LVDS Channel 1 Clock Negative Output 2) LVDSCN

133 VSUP3.3LVDS – Supply Digital Voltage LVDS2), 3.3 V 3.3V

134 LVDSA_2P O LVDS Channel 1 bit 2 Positive Output 2) LVDS2P

135 LVDSA_2N O LVDS Channel 1 bit 2 Negative Output 2) LVDS2N

136 GND3.3LVDS – Ground Digital LVDS2), 3.3 V GND

137 LVDSA_1P O LVDS Channel 1 bit 1 Positive Output 2) LVDS1P

138 LVDSA_1N O LVDS Channel 1 bit 1 Negative Output 2) LVDS1N

139 VSUP3.3LVDS – Supply Digital Voltage LVDS2), 3.3 V 3.3V

140 LVDSA_0P O LVDS Channel 1 bit 0 Positive Output 2) LVDS0P

141 LVDSA_0N O LVDS Channel 1 bit 0 Negative Output 2) LVDS0N

142 VSUP1.8LVDS – Supply Analog Voltage LVDS2), 1.8 V 1.8V

143 REXT – LVDS External Resistor2) REXT

144 GND1.8LVDS – Ground Analog LVDS2), 1.8 V GND

145 LVDSB_3P O Dual-LVDS Channel 2 bit 3 Positive Output 2) Open

146 LVDSB_3N O Dual-LVDS Channel 2 bit 3 Negative Output 2) Open

147 GND3.3LVDS – Ground Digital LVDS2), 3.3 V GND

148 LVDSBCLKP O Dual-LVDS Channel 2 Clock Positive Output 2) Open

149 LVDSBCLKN O Dual-LVDS Channel 2 Clock Negative Output 2) Open

150 VSUP3.3LVDS – Supply Digital Voltage LVDS2), 3.3 V 3.3V

151 LVDSB_2P O Dual-LVDS Channel 2 bit 2 Positive Output 2) Open

152 LVDSB_2N O Dual-LVDS Channel 2 bit 2 Negative Output 2) Open

153 GND3.3LVDS – Ground Digital LVDS2), 3.3 V GND

154 LVDSB_1P O Dual-LVDS Channel 2 bit 1 Positive Output 2) Open

155 LVDSB_1N O Dual-LVDS Channel 2 bit 1 Negative Output 2) Open

156 VSUP3.3LVDS – Supply Digital Voltage LVDS2), 3.3 V 3.3V

157 LVDSB_0P O Dual-LVDS Channel 2 bit 0 Positive Output 2) Open

158 LVDSB_0N O Dual-LVDS Channel 2 bit 0 Negative Output 2) Open

Pin No. Pin Name I/O Pin Function Sheet Name

Loading...

Loading...