LC-26SA1E/RU, LC-32SA1E/RU

7 – 15

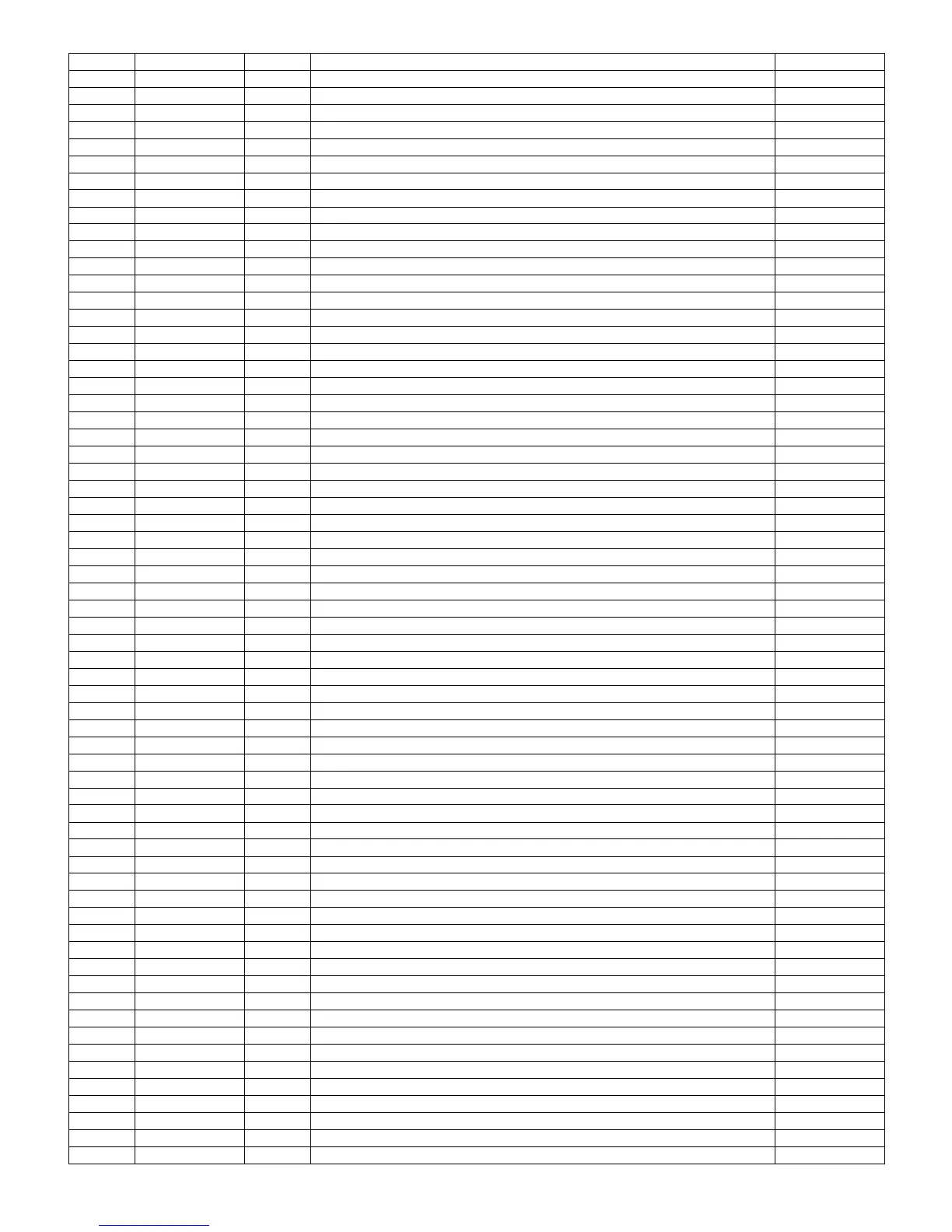

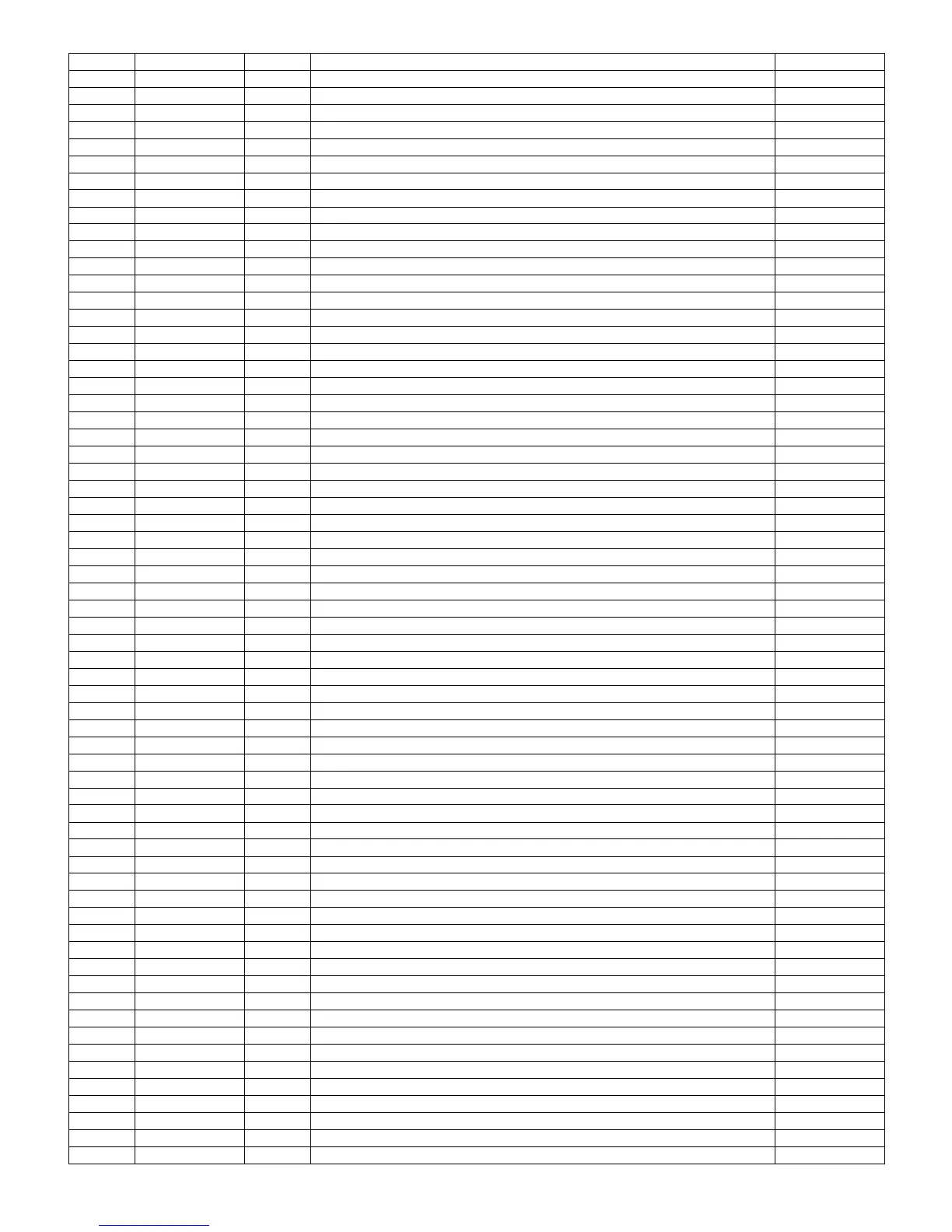

21 GND* – N.C. N.C.

22 #TMS I Pin for JTAG write FPGA_TMS

23 #TDI I Pin for JTAG write FPGA_TDI

24 #TCK I Pin for JTAG write FPGA_TCK

25 #TDO O Pin for JTAG write FPGA_TDO

26 VSYNC I V sync input (not used) V_SYNC

27 HSYNC I H sync input (not used) H_SYNC

28 GND* – N.C. N.C.

29 GND* – N.C N.C.

30 DMY_IN I Dummy pin for RESET line wiring (no effect on operation) RESET_N

31 VCCIO1 – VCC (3.3V) FPGA_VCC

32 GNDIO – Ground. Ground.

33 GND* – N.C. N.C.

34 GND* – N.C. N.C.

35 SCK I Microprocessor control bus clock SCK

36 GND* – N.C. N.C.

37 GND* – N.C. N.C.

38 GND* – N.C. N.C.

39 GND* – N.C. N.C.

40 GND* – N.C. N.C.

41 SEN I Microprocessor control bus enable SDE

42 SDA I Microprocessor control bus data SDA

43 GND* – N.C. N.C.

44 GND* – N.C. N.C.

45 VCCIO1 – VCC (3.3V) FPGA_VCC

46 GNDIO – Ground. Ground.

47 GND* – N.C. N.C.

48 GND* – N.C. N.C

49 GND* – N.C. N.C.

50 GND* – N.C. N.C.

51 GND* – N.C. N.C.

52 GND* – N.C. N.C.

53 GND* – N.C. N.C.

54 GND* – N.C. N.C.

55 GND* – N.C. N.C.

56 GND* – N.C. N.C.

57 GND* – N.C. N.C.

58 GND* – N.C. N.C.

59 VCCIO2 – VCC (3.3V) FPGA_VCC

60 GNDIO – Ground. Ground.

61 GND* – Ground. N.C.

62 GND* – Ground. Ground.

63 VCCINT – VCC (3.3V) FPGA_VCC

64 GND* – Ground. Ground.

65 GNDINT – Ground. Ground.

66 GND* – N.C. N.C.

67 GND* – N.C N.C.

68 GND* – N.C N.C.

69 GND* – N.C N.C.

70 GND* – N.C N.C.

71 GND* – N.C N.C.

72 GND* – N.C N.C.

73 GND* – N.C N.C.

74 GND* – N.C N.C.

75 GND* – N.C N.C.

76 EXP [1] O Outport [1] EP1

77 GND* – N.C

N.C.

78

GND* – N.C. N.C.

79 GNDIO – Ground. Ground.

80 VCCIO2 – VCC (3.3V) FPGA_VCC

81 GND* – N.C. N.C

82 GND* – N.C. N.C

83 GND* – N.C. N.C

84 GND* – N.C. N.C

Pin No. Pin Name I/O Pin Function Sheet Name

Loading...

Loading...