1 Technical Description

1.5 Functional Description

1.5.8 Complex Functions (Arithmetic blocks c, d, h)

Manual

68

SIP ART DR24 6DR2410

C79000-G7476-C153-03

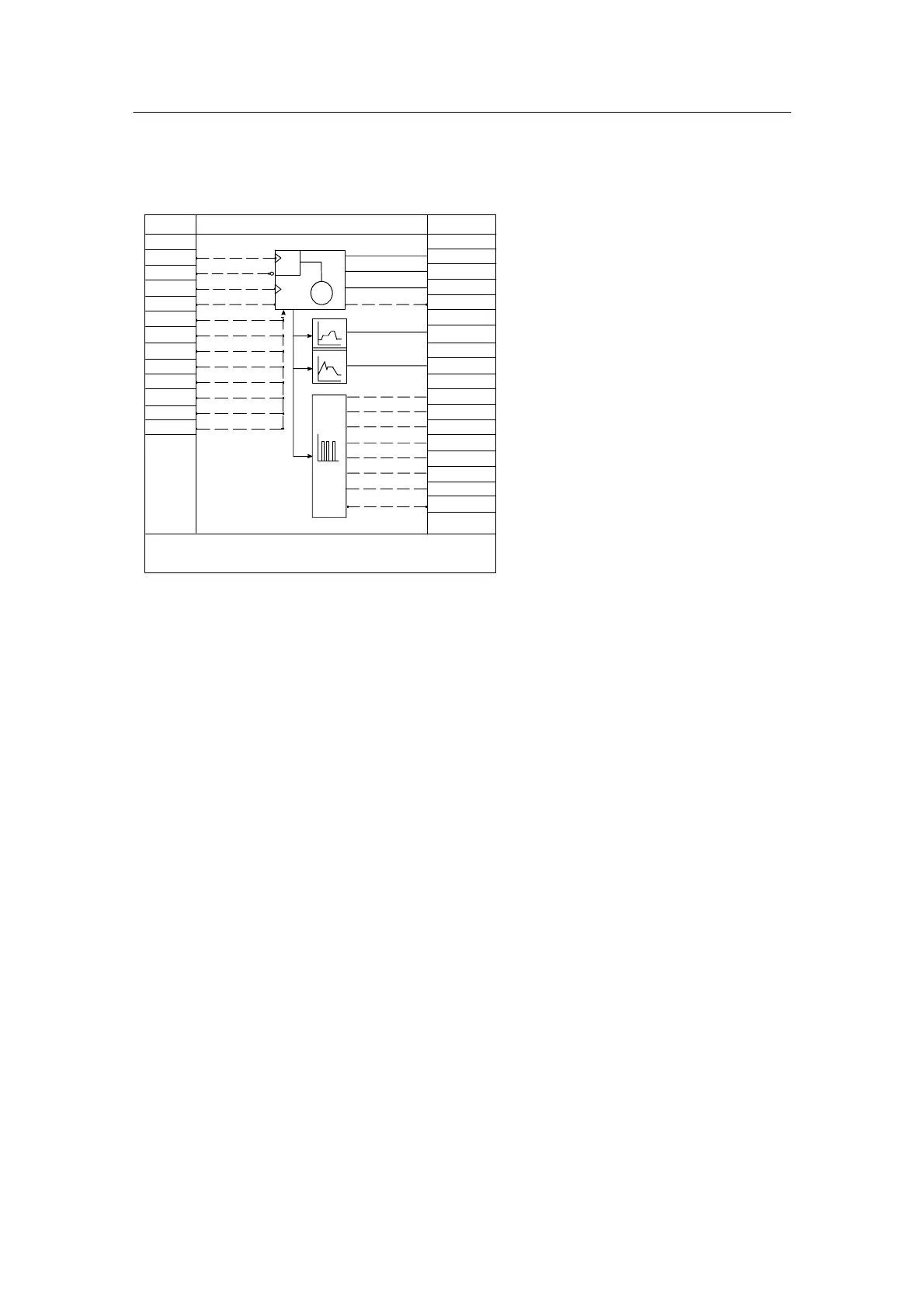

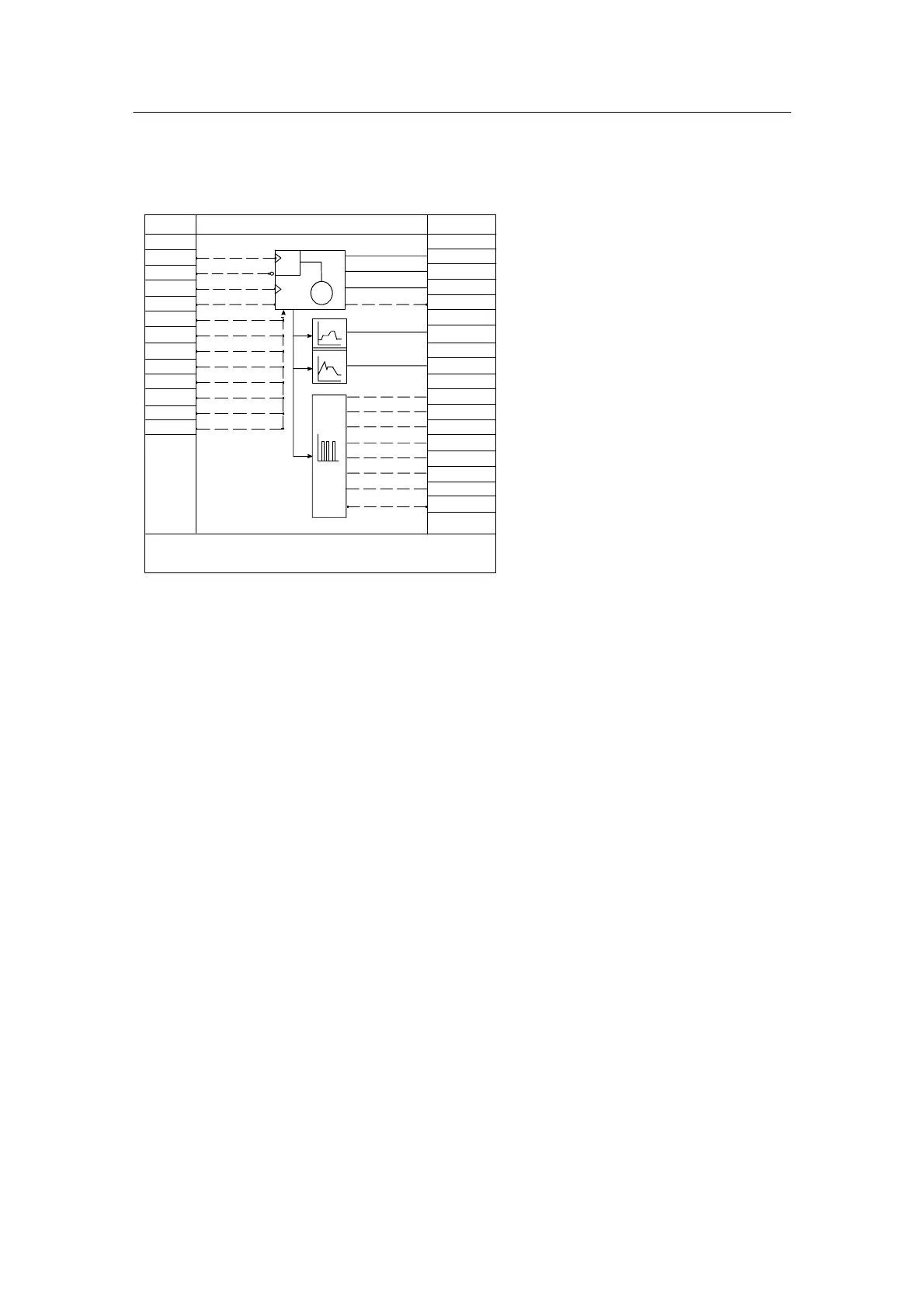

Clock CLoc

b1

b2

b3

b4

b5

b6

b7

b8

Lo

Time from start

Time in interval

Interval

Clock stop

Start

Stop

Reset

Fast

Preselec. v. SES

”Pr.2

”.3

”4

”5

”5

”7

Preselec. Pr. 8

Lo

ncon

A2

A1

Lo

Lo

Lo

Lo

Lo

Lo

Lo

Lo

Lo

# .01

# .02

# .03

# .04

# .05

# .06

# .07

# .08

# .09

# .10

# .11

# .12

CLoc.1

.1A ∩

.2A ∩

.3A ∩

.4A #

.5A ∩

.6A ∩

.7A #

.8A #

.9A #

.10.(A)#

.11.(A)#

.12.(A)#

.13.(A)#

.14.(A)#

(CLPA)

CLFo,CLCY,CLSb,CLPr,CLti

CLA1,2 CLb1...8

&

<

d0_.F

n

---

Consecutive number

of the arithmetic block

No. in the cycle

The clock can be defined once in FdEF in the arithmetic blocks d0*.F. T wo analog outputs and

8 digital outputs can be assigned to a common timebase -- with a maximum 40 time intervals --

with the clock.

These 40 intervals can be distributed between up to 8 independent sub--routines. An appropri-

ate number of intervals is assigned to the programs CLPr 1 to 8. (parameter CLPr).

The time intervals of the programs are entered per interval according to the selected clock for-

mat (private parameter CLFo) in [h, min] or [min, s] (private parameter CLti). Then the time in-

tervals are assigned the values for the analog outputs (private parameter CLA*) or the status of

the digital outputs (private parameter CLb*). The programs defined in CLPr can run once, sev-

eral times or cyclically (private parameter CLCY). The clock process can be accelerated in

steps for test purposes (private parameter CLSb). The clock is controlled by the inputs Start,

Stop, Reset and Fast.

The controlling source for the program preselection is defined with d*.05.

d*.05 = low preselection through the inputs d*.06 to d*.12

d*.05 = high preselection through the SES (Status ST--CLOCK)

If the inputs d*.06 to d*.12 are low , the 1st program runs after Start. A high signal at one of the

preselection inputs d*.06 to d*.12 defines the program 2 to 8 to be processed which is activated

with the edge Start = Low/High. The time process can be monitored by the outputs time from

Start, time in the interval, interval display and Clock stop.

The following components are described in detail below:

D Private parameters

D Inputs d*.01 to d*.12

D Outputs d*.1A to d*.14.(A)

Loading...

Loading...