15

CDX-CA850/CA850X/CA860X

SECTION 3

DIAGRAMS

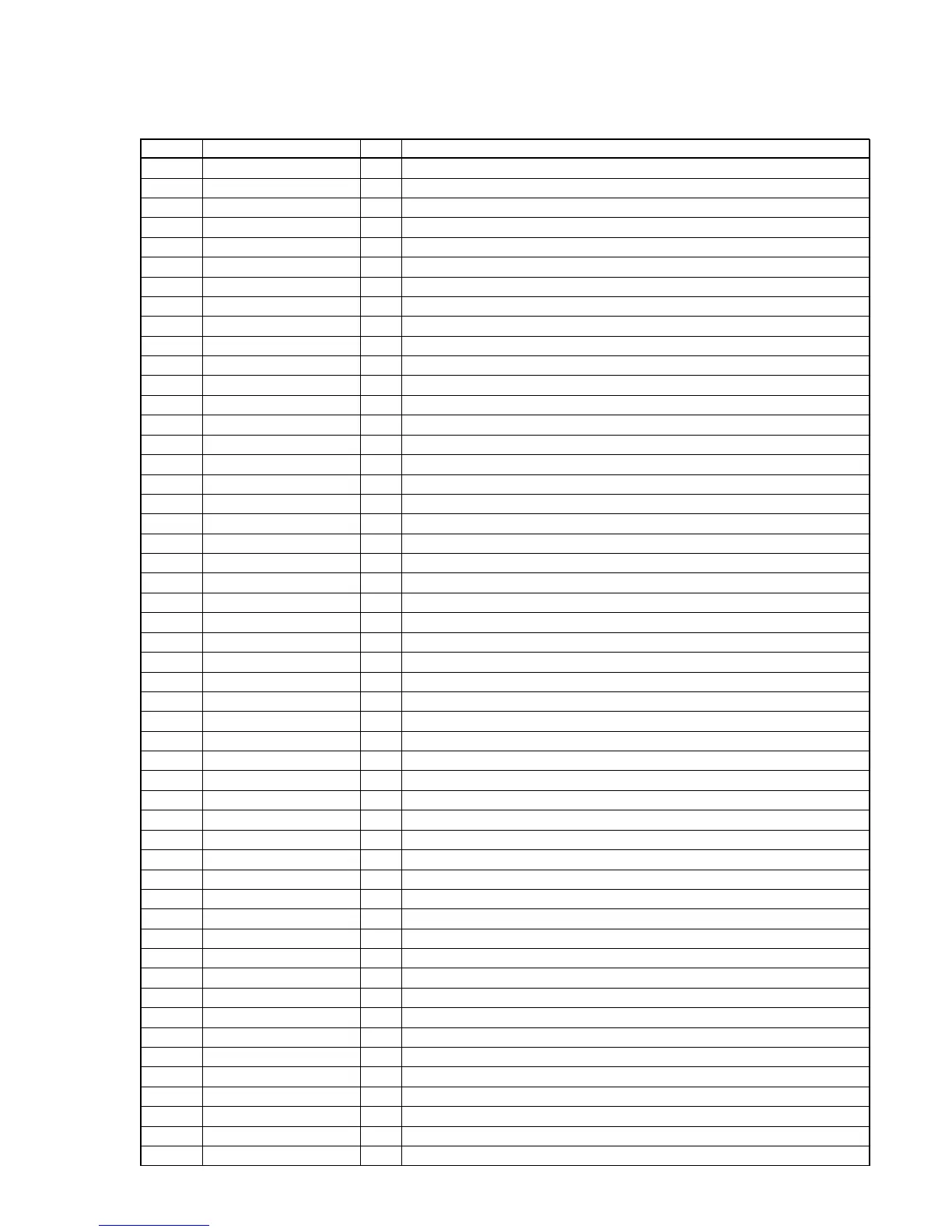

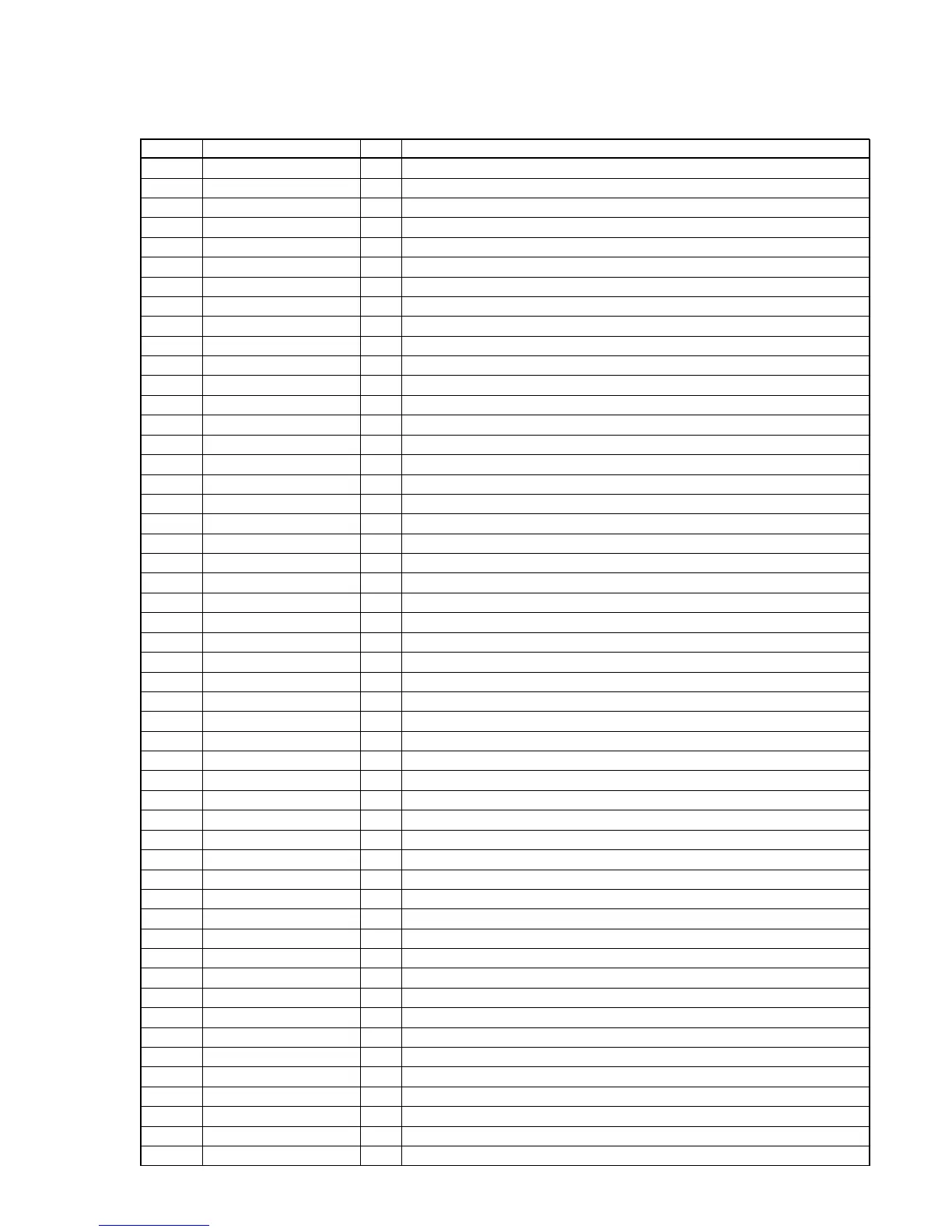

3-1. IC PIN DESCRIPTIONS

• IC501 CXD2598Q (DIGITAL SERVO, DIGITAL SIGNAL PROCESSOR) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 DVDD — Digital power supply pin

2 DVSS — Digital ground

3 SOUT O Servo brock serial data output (Not used.)

4 SOCK O Servo brock serial data read clock output (Not used.)

5 XOLT O Servo brock serial data latch output (Not used.)

6 SQSO O Sub Q 80 bit, PCM peak and level data output. CD TEXT data output

7 SQCK I Clock input from SQSO read output.

8 SCSY I Fixed at “L”.

9 SBSO O Serial output of sub-P to W. (Not used.)

10 EXCK I Clock input from SBSO read output. (Fixed at “L”)

11 XRST I System reset (“L”: Reset)

12 STSM I System mute input (Fixed at “L”)

13 DATA I Serial data input from CPU.

14 XLAT I Latch input from CPU. Latch serial data at the falling edge.

15 CLOK I Serial data transfer clock input from CPU.

16 SENS O SENS output for CPU.

17 SCLK I Clock input from SENS serial data read.

18 ATSK I/O Input/output for anti-shock.

19 WFCK O WFCK (Write Flame Clock) output (Not used.)

20 XUGF O XUGF output (Not used.)

21 XPCK O XPCK output (Not used.)

22 GFS O GFS output

23 C2PO O C2PO output (Not used.)

24 SCOR O “H” output at either detection, sub code sync S0 or S1.

25 C4M O 4.2336 MHz output (Not used.)

26 WDCK O Word clock input f=2Fs (Not used.)

27 COUT I/O Track number count signal input/output (Not used.)

28 MIRR I/O Mirror signal input/output (Not used.)

29 DVSS — Digital ground

30 DVDD — Digital power supply pin

31 DFCT I/O Diffect signal input/output (Not used.)

32 FOK I/O Focus OK signal output

33 PWM1 I External control input of spindle motor.

34 LOCK I/O Lock signal input/output

35 MDP O Servo control output of spindle motor.

36 SSTP I Disc most inner track detection signal input

37 FSTIO I/O 2/3 frequency division output of pins ih and ij. (Not used.)

38 SFDR O Sled drive output

39 SRDR O Sled drive output

40 TFDR O Tracking drive output

41 TRDR O Tracking drive output

42 FFDR O Focus drive output

43 FRDR O Focus drive output

44 DVDD — Digital power supply pin

45 DVSS — Digital ground

46 TEST I Test pin (Fixed at “L”)

47 TES1 I Test pin (Fixed at “L”)

48 XTSL I X’tal select input (“L”: 16.9344 MHz, “H”: 33.8688 MHz)

49 VC I Center voltage input

50 FE I Focus error signal input

51 SE I Sled error signal input

Loading...

Loading...