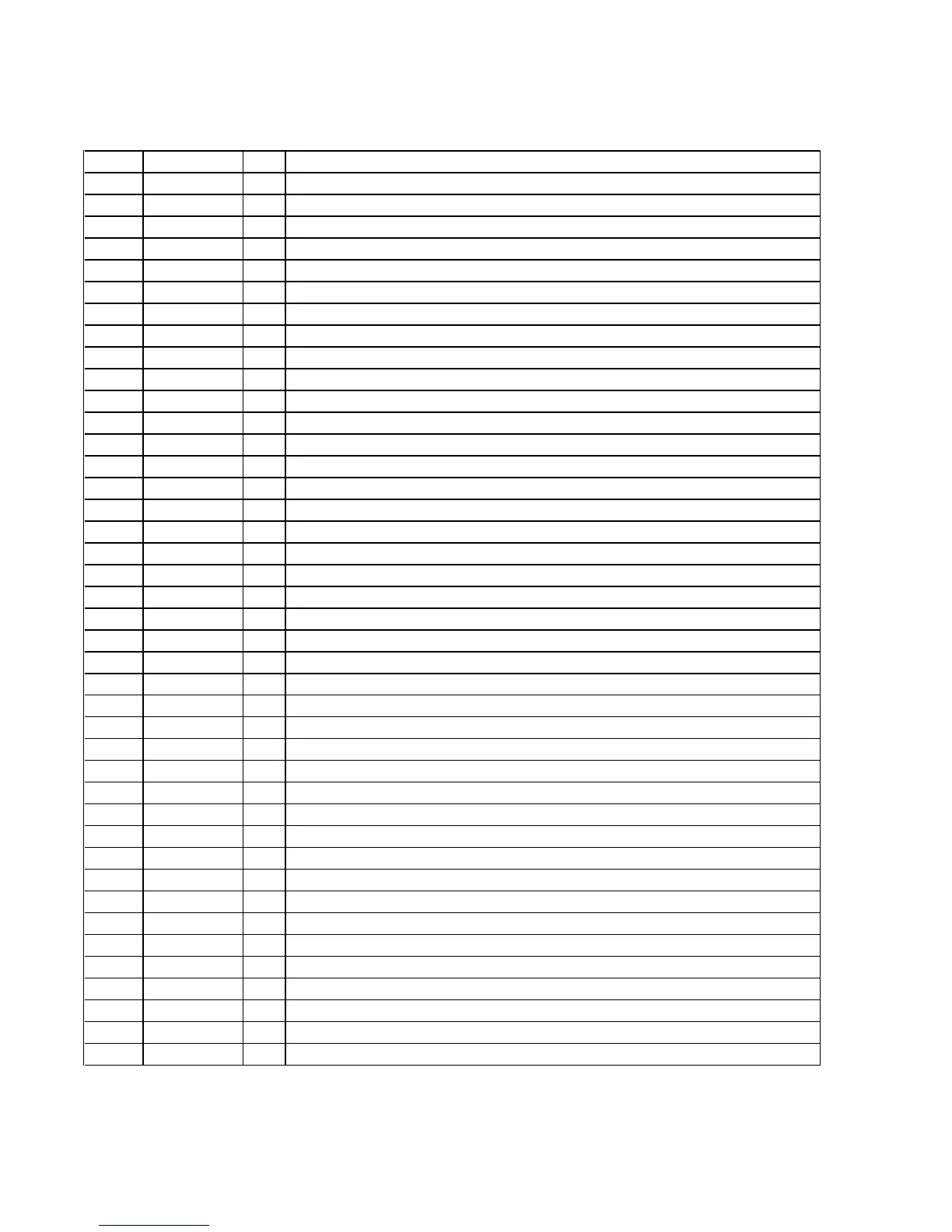

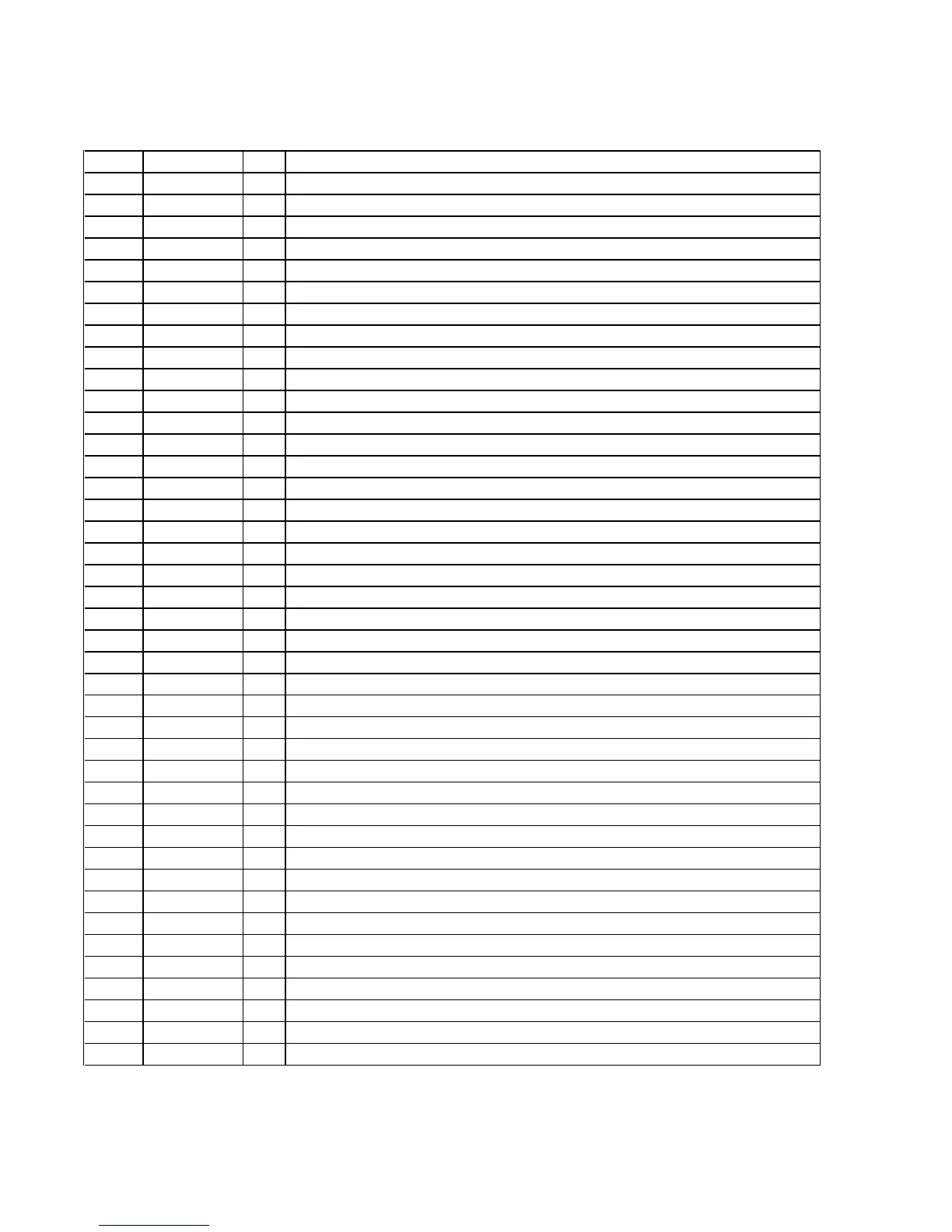

50

DVP-S9

Pin No. Pin Name I/O Description

51 XIFCS O

Chip select signal output to the interface controller (IC401)

52 VSS —

Ground terminal

53 X1 O

System clock output terminal (16.5MHz)

54 X0 I

System clock input terminal (16.5MHz)

55 VCC —

Power supply terminal (+3.3V)

56 CKSW1 —

Not used (open)

57 OCSSW1 —

Not used (open)

58 CS0X O

Chip select signal output to the flash memory (IC107)

59 CS1X —

Not used (open)

60 CS2X O

Chip select signal output to the AV decoder (IC503)

61 CS3X O

Chip select signal output to the AV decoder (IC503)

62 CS4X O

Chip select signal output to the ARP (IC302)

63 CS5X O

Chip select signal output to the Servo DSP (IC302)

64 C —

Capacitor connected terminal

65 CS6X O

Chip select signal output to the gate array (IC202)

66 CS7X —

Not used (open)

67 XWAIT I

Wait signal input terminal

68 BGRNTX —

Not used (fixed at “H”)

69 BGR —

Not used (open)

70 XRD O

Read enable signal output terminal

71 XWRH O

High byte write enable signal output terminal

72 XWRL —

Not used (open)

73 NMIX —

Not used (fixed at “H”)

74 HSTX —

Not used (fixed at “H”)

75 VSS —

Ground terminal

76 XFRRST I

Reset signal input from the interface controller (IC401) “L”: reset

77 CPUCK O

CPU clock signal output terminal

78 OCSW2 —

Not used (fixed at “H”)

79 XDACX —

Not used (fixed at “H”)

80 VESCS/X39CS —

Not used (fixed at “H”)

81 48/44.1K O

Sampling frequency selection signal output terminal “L”: 48kHz, “H”: 44.1kHz

82 WIDE O

Wide signal output terminal

83 MAMUTE I

System OK signal input terminal

84 XLDON O

LD control signal output terminal

85 to 100 HD0 to HD15 I/O

Two-way data bus terminal

101 VSS —

Ground terminal

102 to 10

HA0 to HA7 O

Address signal output terminal

110 VCC —

Power supply terminal (+3.3V)

111 to 118 HA8 to HA15 O

Address signal output terminal

119 VSS —

Ground terminal

120 HA16 O

Address signal output terminal

Loading...

Loading...