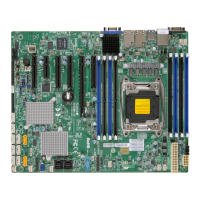

2-30

X10SLH-LN6TF User’s Manual

A

IPMI CODE

CA

BIOS

LICENSE

BAR CODE

MAC CODE

CA

A

C

A

C

A

+

JLAN3

JLAN2

JLAN1

JP1000

JPW1

JPW2

JSTBY1

J4

LE6

DIMM1

DIMM2

DIMM4

DIMM3

FAN4

FAN3

FAN2

FAN1

FANA

JPME1

JI2C1

JPME2

JI2C2

JPUSB1

JPL1

JPL2

JPL3

JPG1

JBR1

JWD1

JLED1

LE5

LE4

LE1

LE3

J3

JL1

JLED_LAN4

JLED_LAN3

JLED_LAN6

JLED_LAN5

JPI2C1

JTPM1

T-SGPIO1

T-SGPIO2

JSD2

JSD1

SPKR1

B1

JBT1

JF1

SW1

COM1

COM2

PCH SLOT4 PCI-E 2.0 X4(IN X8)

DESIGNED IN USA

X10SLH-LN6TF

REV:1.01

USB0(3.0)

USB1(3.0)

USB12/13

USB8/9

CPU SLOT6 PCI-E 3.0 X8(IN X16)

I-SATA0

I-SATA2

I-SATA1

I-SATA3

I-SATA4

I-SATA5

VGA

LAN5/6

LAN3/4

LAN1/2

USB4/5 (2.0)

USB2/3(3.0)

JLED1:3 pin Power LED

IPMI LAN

JF1

NIC2

NIC1

ON

PWR

X

RST

OH/

FF

LED

LED

HDD

X

PWR

NMI

C226

X540

X540

X540

BMC

PLX

C

A.T-SGPIO 1

B.T-SGPIO 2

C.JTPM1

A

B

T-SGPIO 1/2 Headers

Two Serial-Link General Purpose

Input/Output headers (T-SGPIO 1/2)

are located on the motherboard to en-

hance system performance. See the

table on the right for pin denitions.

Note: NC= No Connection

T-SGPIO

Pin Denitions

Pin# Denition Pin Denition

1 NC 2 NC

3 Ground 4 Data

5 Load 6 Ground

7 Clock 8 NC

TPM Header/Port 80 Header

A Trusted Platform Module/Port 80

header is located at JTPM1 to provide

TPM support and Port 80 connection.

Use this header to enhance system

performance and data security. See

the table on the right for pin deni-

tions.

TPM/Port 80 Header

Pin Denitions

Pin # Denition Pin # Denition

1 LCLK 2 GND

3 LFRAME# 4 <(KEY)>

5 LRESET# 6 +5V (X)

7 LAD 3 8 LAD 2

9 +3.3V 10 LAD1

11 LAD0 12 GND

13 SMB_CLK4 14 SMB_DAT4

15 +3V_DUAL 16 SERIRQ

17 GND 18 CLKRUN# (X)

19 LPCPD# 20 LDRQ# (X)

Loading...

Loading...