48 Description TM8100/TM8200 Service Manual

© Tait Electronics Limited June 2006

Software Start-Up

When the radio is turned on, the following processes are carried out on the

main board:

Note This process describes the software start-up into normal radio

operation mode.

1. The FPGA image, which includes the RISC processor and the cus-

tom logic, is loaded from the serial flash to the FPGA.

2. The RISC processor executes the boot code, which carries out an

initialization and auto-calibration, and—in the case of a fault—

generates an error code for display on the control head.

3. Normal radio operation starts with:

■ the RISC processor executing the radio application code,

including application software

■ the DSP executing the DSP code for processing of digital signals

■ the custom logic executing additional digital signal processing.

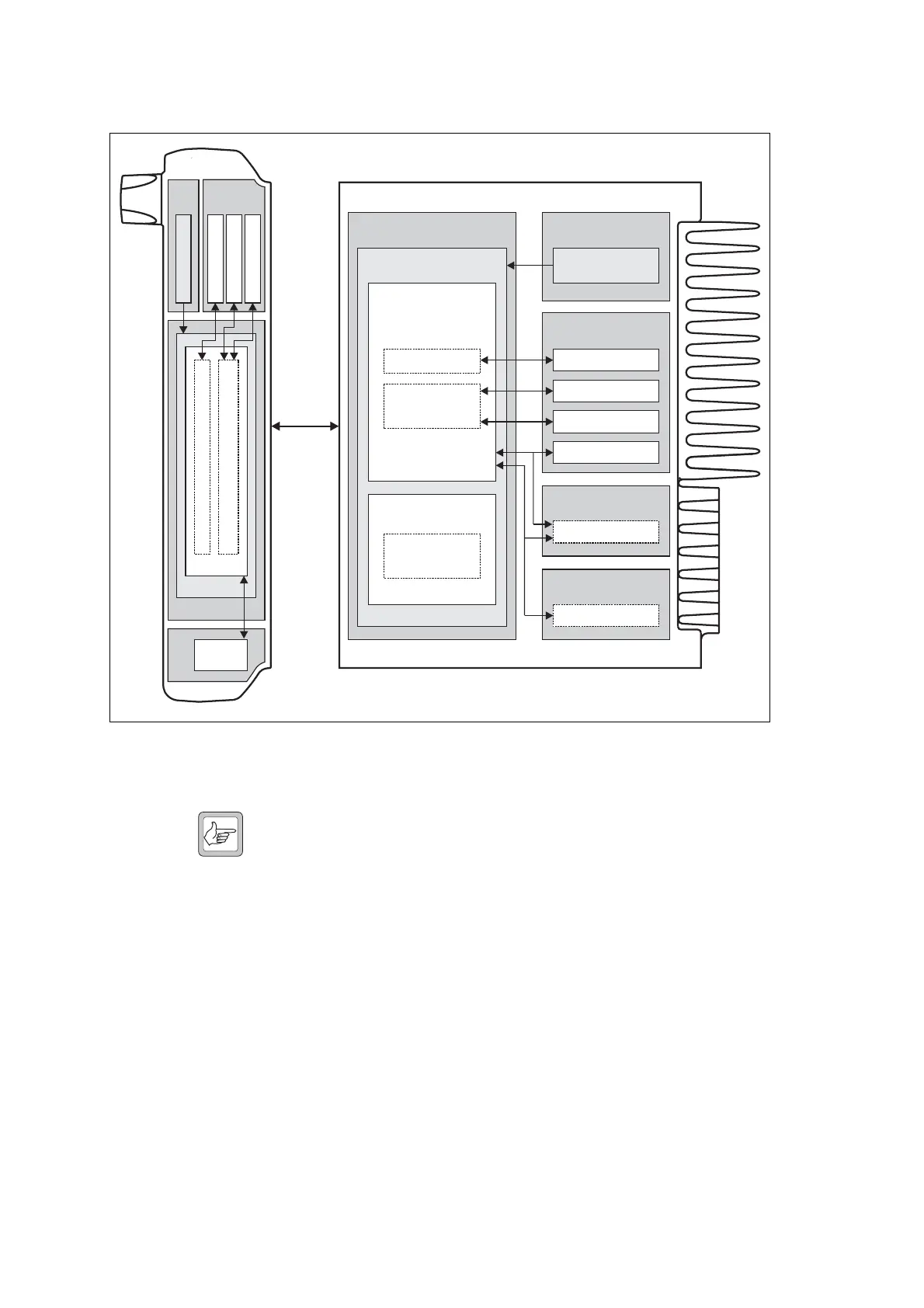

Figure 2.15 Software architecture (radio with graphical-display control head shown)

FPGA

SRAM

Dynamic

Memory

FPGA Image

RISC Proc.

Control-Head Application Code

FPGA Image

Boot Code

Serial

Flash

Database

Boot Code

Flash

Memory

Application Code

FPGA

Radio Application

Code

Serial Flash

Radio Application Code

Custom Logic

Additional Digital

Signal Processing

FPGA Image

FPGA Image

RISC Processor

Boot Code

DSP

DSP Code

Flash Memory

Boot Code

Database

DSP Code

SRAM

Dynamic Memory

Loading...

Loading...